## Ryerson University Department of Electrical and Computer Engineering COE 608–Computer Organization and Architecture

| Final ExamAPRIL 27, 2016                                                                                                 |                 |                         |

|--------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------|

| Name:                                                                                                                    | Student Number: | Sec:                    |

| Time limit: 2 hours 30 min                                                                                               |                 | Examiners: N. Mekhiel   |

| <ul><li>Notes:</li><li>a) Closed book.</li><li>b) No calculators.</li><li>c) Answer all questions in the space</li></ul> | ce provided.    | Total Marks=80, each=20 |

Q1-1 Translate the following into C. Assume i is in register \$s2, \$s0 has base address of A[] array, \$s1 has base address of B[] array and register \$s9 has 1000.

addi \$s2, \$0, \$0 LOOP: sll \$s3, \$s2, 2 add \$s4, \$s0, \$s3 add \$s5, \$s1, \$s3 lw \$s6, 0(\$s4) lw \$s7, 0(s5) add \$s8, \$s7, \$s6 sw \$s8, 0(\$s4) addi \$s2, \$s2, 1 beq \$s2, \$s9, EXIT j LOOP EXIT:

Section:\_\_\_\_

Q1-2 Find the effective CPI for the above code if arithmetic and logic operations take 1 cycle, data transfer instructions take 3 cycles, and conditional branches take 2 cycles, unconditional branches takes 1 cycle.

Q1-3 Calculate the performance of the above code if the MIPS processor runs at 1 GHz

Q1-4 Find performance of above code if MIPS uses on chip cache for data transfers that improves it by 3 times but it slows down processor speed to 800 MHz.

Section:\_\_\_\_

Q2-1 Design a Register File that consists of 16 Registers, each has 16 bits. Register File must have two READ ports, and one WRITE port. Draw a detailed schematic diagram.

Q2-2 Explain how a READ operations from Register 7, and Register 9 can be performed at the same time

Q2-3 Explain how a WRITE operation of 007E HEX to Register 2 is performed

Q3-1Convert the following decimal to IEEE754 FP format: -.5625

Q3-2 Draw a block diagram (hardware) to implement a multiplier system for 16 bits numbers

Q3-3 Calculate how long it takes for a single multiplication operation in the above syste assuming clock speed is = 1 GHz

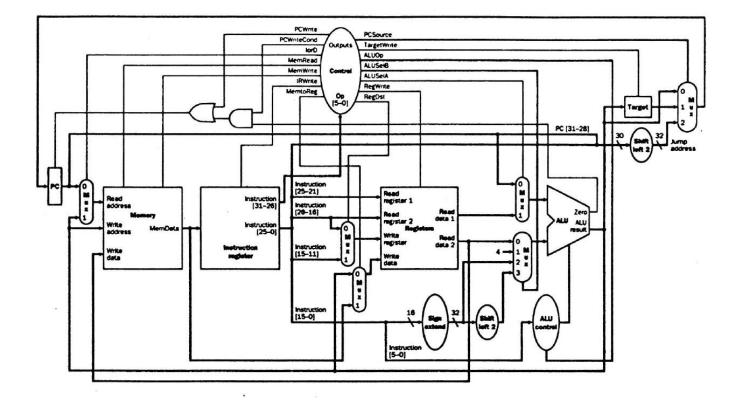

Q4-1 For the Multicycle Data Path below, find the effective CPI running the code of Q1

Q4-2 Find the value of asserted control signals in each cycle when executing the following instruction:

sw \$s8, 0(\$s4)

Q4-3 Identify all types of Hazards in the code of Q1 if it runs in a pipeline data path

Q4-4 If the pipeline uses forwarding, identify hazard stalls in Q1 that could not be eliminated by forwarding, then suggest a solution to get rid of stalls

Name: