#### PROGRAMMER'S GUIDE AND INSTRUCTION SET

#### **Memory Organization**

#### Program Memory

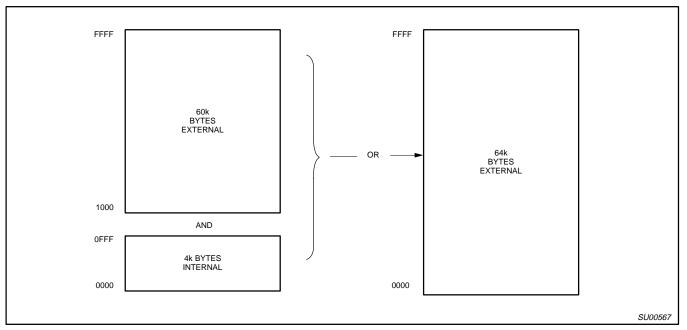

The 80C51 has separate address spaces for program and data memory. The Program memory can be up to 64k bytes long. The lower 4k can reside on-chip. Figure 1 shows a map of the 80C51 program memory.

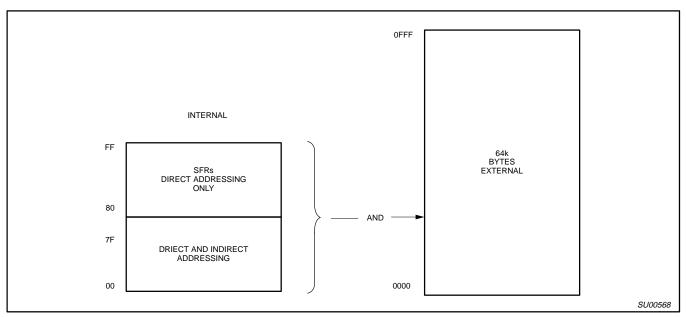

The 80C51 can address up to 64k bytes of data memory to the chip. The MOVX instruction is used to access the external data memory.

The 80C51 has 128 bytes of on-chip RAM, plus a number of Special Function Registers (SFRs). The lower 128 bytes of RAM can be accessed either by direct addressing (MOV data addr) or by indirect addressing (MOV @Ri). Figure 2 shows the Data Memory organization.

#### **Direct and Indirect Address Area**

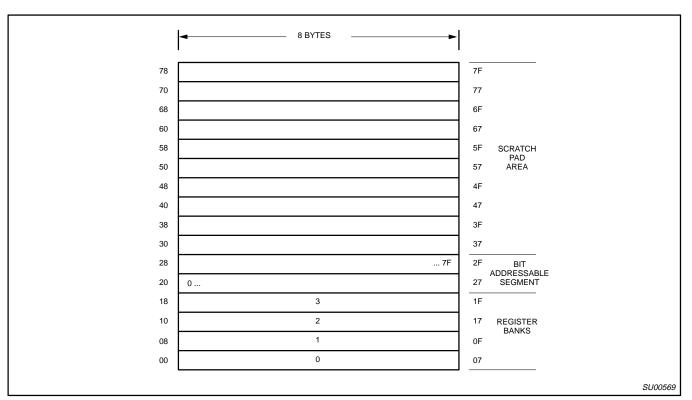

The 128 bytes of RAM which can be accessed by both direct and indirect addressing can be divided into three segments as listed below and shown in Figure 3.

- Register Banks 0-3: Locations 0 through 1FH (32 bytes). The device after reset defaults to register bank 0. To use the other register banks, the user must select them in software. Each register bank contains eight 1-byte registers 0 through 7. Reset initializes the stack pointer to location 07H, and it is incremented once to start from location 08H, which is the first register (R0) of the second register bank. Thus, in order to use more than one register bank, the SP should be initialized to a different location of the RAM where it is not used for data storage (i.e., the higher part of the RAM).

- 2. Bit Addressable Area: 16 bytes have been assigned for this segment, 20H-2FH.

Each one of the 128 bits of this segment can be directly addressed (0-7FH). The bits can be referred to in two ways, both of which are acceptable by most assemblers. One way is to refer to their address (i.e., 0-7FH). The other way is with reference to bytes 20H to 2FH. Thus, bits 0-7 can also be referred to as bits 20.0-20.7, and bits 8-FH are the same as 21.0-21.7, and so on. Each of the 16 bytes in this segment can also be addressed as a byte.

3. Scratch Pad Area: 30H through 7FH are available to the user as data RAM. However, if the stack pointer has been initialized to this area, enough bytes should be left aside to prevent SP data destruction.

Figure 2 shows the different segments of the on-chip RAM.

Figure 1. 80C51 Program Memory

Figure 2. 80C51 Data Memory

Figure 3. 128 Bytes of RAM Direct and Indirect Addressable

# 80C51 family programmer's guide and instruction set

| SYMBOL            | DESCRIPTION               | DIRECT<br>ADDRESS | BIT AD<br>MSB | DRESS, | SYMBO | L, OR AL | TERNAT | IVE POR | T FUNCT | ION<br>LSB | RESET VALUE |

|-------------------|---------------------------|-------------------|---------------|--------|-------|----------|--------|---------|---------|------------|-------------|

| ACC*              | Accumulator               | E0H               | E7            | E6     | E5    | E4       | E3     | E2      | E1      | E0         | 00H         |

| B*                | B register                | F0H               | F7            | F6     | F5    | F4       | F3     | F2      | F1      | F0         | 00H         |

| DPTR              | Data pointer (2<br>bytes) |                   |               |        |       |          |        |         |         |            |             |

| DPH               | Data pointer high         | 83H               |               |        |       |          |        |         |         |            | 00H         |

| DPL               | Data pointer low          | 82H               |               |        |       |          |        |         |         |            | 00H         |

|                   |                           |                   | AF            | AE     | AD    | AC       | AB     | AA      | A9      | A8         |             |

| IE*               | Interrupt enable          | A8H               | EA            | -      | -     | ES       | ET1    | EX1     | ET0     | EX0        | 0x000000B   |

|                   |                           |                   | BF            | BE     | BD    | BC       | BB     | BA      | B9      | B8         |             |

| IP*               | Interrupt priority        | B8H               | -             | -      | -     | PS       | PT1    | PX1     | PT0     | PX0        | xx000000B   |

|                   |                           |                   |               |        |       |          |        |         |         |            |             |

|                   |                           |                   | 87            | 86     | 85    | 84       | 83     | 82      | 81      | 80         |             |

| P0*               | Port 0                    | 80H               | AD7           | AD6    | AD5   | AD4      | AD3    | AD2     | AD1     | AD0        | FFH         |

|                   |                           |                   |               |        |       |          |        |         |         |            |             |

|                   |                           |                   | 97            | 96     | 95    | 94       | 93     | 92      | 91      | 90         |             |

| P1*               | Port 1                    | 90H               | -             | -      | -     | -        | -      | -       | T2EX    | T2         | FFH         |

|                   |                           |                   |               |        |       |          |        |         |         |            |             |

|                   |                           |                   | A7            | A6     | A5    | A4       | A3     | A2      | A1      | A0         |             |

| P2*               | Port 2                    | A0H               | A15           | A14    | A13   | A12      | A11    | A10     | A9      | A8         | FFH         |

|                   |                           |                   |               |        |       |          |        |         |         |            |             |

|                   |                           |                   | B7            | B6     | B5    | B4       | B3     | B2      | B1      | B0         |             |

| P3*               | Port 3                    | B0H               | RD            | WR     | T1    | то       | INT1   | INTO    | TxD     | Rxd        | FFH         |

| PCON <sup>1</sup> | Power control             | 87H               | SMOD          | -      | -     | -        | GF1    | GF0     | PD      | IDL        | 0xxxxxxB    |

|                   |                           |                   |               |        |       |          |        |         |         |            |             |

|                   |                           |                   | D7            | D6     | D5    | D4       | D3     | D2      | D1      | D0         |             |

| PSW*              | Program status word       | D0H               | CY            | AC     | F0    | RS1      | RS0    | OV      | -       | Р          | 00H         |

| SBUF              | Serial data buffer        | 99H               |               |        |       |          |        |         |         |            | xxxxxxxB    |

|                   |                           |                   | 9F            | 9E     | 9D    | 9C       | 9B     | 9A      | 99      | 98         |             |

| SCON*             | Serial controller         | 98H               | SM0           | SM1    | SM2   | REN      | TB8    | RB8     | ТІ      | RI         | 00H         |

| SP                | Stack pointer             | 81H               |               |        |       |          |        |         |         |            | 07H         |

|                   |                           |                   | 8F            | 8E     | 8D    | 8C       | 8B     | 8A      | 89      | 88         |             |

| TCON*             | Timer control             | 88H               | TF1           | TR1    | TF0   | TR0      | IE1    | IT1     | IE0     | IT0        |             |

| TH0               | Timer high 0              | 8CH               |               |        |       |          |        |         |         |            | 00H         |

| TH1               | Timer high 1              | 8DH               |               |        |       |          |        |         |         |            | 00H         |

| TL0               | Timer low 0               | 8AH               |               |        |       |          |        |         |         |            | 00H         |

| TL1               | Timer low 1               | 8BH               |               |        |       |          |        |         |         |            | 00H         |

| TMOD              | Timer mode                | 89H               | GATE          | C/T    | M1    | MO       | GATE   | C/T     | M1      | MO         | 00H         |

### Table 1. 80C51 Special Function Registers

NOTES:

\* Bit addressable

1. Bits GF1, GF0, PD, and IDL of the PCON register are not implemented on the NMOS 8051/8031.

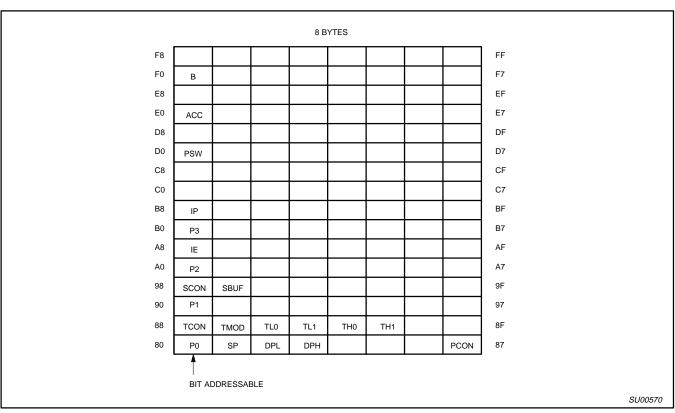

Figure 4. SFR Memory Map

Those SFRs that have their bits assigned for various functions are listed in this section. A brief description of each bit is provided for quick reference. For more detailed information refer to the Architecture Chapter of this book.

#### **PSW: PROGRAM STATUS WORD. BIT ADDRESSABLE.**

| CY  | AC    | F0   | RS1                                               | RS0               | OV         | -           | Р            |  |  |

|-----|-------|------|---------------------------------------------------|-------------------|------------|-------------|--------------|--|--|

| CY  | PSW.7 | Carr | y Flag.                                           |                   |            |             |              |  |  |

| AC  | PSW.6 | Auxi | Auxiliary Carry Flag.                             |                   |            |             |              |  |  |

| F0  | PSW.5 | Flag | Flag 0 available to the user for general purpose. |                   |            |             |              |  |  |

| RS1 | PSW.4 | Regi | Register Bank selector bit 1 (SEE NOTE 1).        |                   |            |             |              |  |  |

| RS0 | PSW.3 | Regi | ster Bank                                         | selector bit      | t 0 (SEE N | OTE 1).     |              |  |  |

| OV  | PSW.2 | Over | flow Flag.                                        |                   |            |             |              |  |  |

| -   | PSW.1 | Usat | ole as a ge                                       | neral purp        | ose flag.  |             |              |  |  |

| Ρ   | PSW.0 |      | y flag. Set/<br>accumulato                        | cleared by<br>or. | hardware   | each instru | iction cycle |  |  |

#### NOTE:

1. The value presented by RS0 and RS1 selects the corresponding register bank.

| RS1 | RS0 | REGISTER BANK | ADDRESS |

|-----|-----|---------------|---------|

| 0   | 0   | 0             | 00H-07H |

| 0   | 1   | 1             | 08H-0FH |

| 1   | 0   | 2             | 10H-17H |

| 1   | 1   | 3             | 18H-1FH |

#### PCON: POWER CONTROL REGISTER. NOT BIT ADDRESSABLE.

| SMOD – – – | GF1 | GF0 | PD | IDL |

|------------|-----|-----|----|-----|

|------------|-----|-----|----|-----|

SMOD Double baud rate bit. If Timer 1 is used to generate baud rate and SMOD = 1, the baud rate is doubled when the Serial Port is used in modes 1, 2, or 3.

Not implemented, reserved for future use.\*

Not implemented reserved for future use.\*

Not implemented reserved for future use.\*

GF1 General purpose flag bit.

GF0 General purpose flag bit.

PD Power Down Bit. Setting this bit activates Power Down operation in the 80C51. (Available only in CMOS.)

IDL Idle mode bit. Setting this bit activates Idle Mode operation in the 80C51. (Available only in CMOS.)

If 1s are written to PD and IDL at the same time, PD takes precedence.

\* User software should not write 1s to reserved bits. These bits may be used in future 8051 products to invoke new features.

#### INTERRUPTS:

To use any of the interrupts in the 80C51 Family, the following three steps must be taken.

- 1. Set the EA (enable all) bit in the IE register to 1.

- 2. Set the corresponding individual interrupt enable bit in the IE register to 1.

3. Begin the interrupt service routine at the corresponding Vector Address of that interrupt. See Table below.

| INTERRUPT SOURCE | VECTOR ADDRESS |

|------------------|----------------|

| IEO              | 0003H          |

| TF0              | 000BH          |

| IE1              | 0013H          |

| TF1              | 001BH          |

| RI & TI          | 0023H          |

In addition, for external interrupts, pins INT0 and INT1 (P3.2 and P3.3) must be set to 1, and depending on whether the interrupt is to be level or transition activated, bits IT0 or IT1 in the TCON register may need to be set to 1.

ITx = 0 level activated

ITx = 1 transition activated

#### IE: INTERRUPT ENABLE REGISTER. BIT ADDRESSABLE.

If the bit is 0, the corresponding interrupt is disabled. If the bit is 1, the corresponding interrupt is enabled.

| EA  | _    | _     | ES                                                | ET1          | EX1          | ET0         | EX0 |  |  |

|-----|------|-------|---------------------------------------------------|--------------|--------------|-------------|-----|--|--|

| EA  | IE.7 |       | bles all inte<br>idually ena                      |              | ,            |             |     |  |  |

| —   | IE.6 | Not i | mplemente                                         | ed, reserve  | d for futur  | e use.*     |     |  |  |

| —   | IE.5 | Not i | mplemente                                         | ed, reserve  | ed for futur | e use.*     |     |  |  |

| ES  | IE.4 | Enat  | ole or disab                                      | ole the seri | al port inte | rrupt.      |     |  |  |

| ET1 | IE.3 | Enat  | ole or disat                                      | ole the Tim  | er 1 overfle | ow interrup | ot. |  |  |

| EX1 | IE.2 | Enat  | Enable or disable External Interrupt 1.           |              |              |             |     |  |  |

| ET0 | IE.1 | Enat  | Enable or disable the Timer 0 overflow interrupt. |              |              |             |     |  |  |

| EX0 | IE.0 | Enat  | ole or disab                                      | ole Externa  | al Interrupt | 0.          |     |  |  |

\* User software should not write 1s to reserved bits. These bits may be used in future 80C51 products to invoke new features.

#### ASSIGNING HIGHER PRIORITY TO ONE OR MORE INTERRUPTS:

In order to assign higher priority to an interrupt the corresponding bit in the IP register must be set to 1.

Remember that while an interrupt service is in progress, it cannot be interrupted by a lower or same level interrupt.

#### **PRIORITY WITHIN LEVEL:**

Priority within level is only to resolve simultaneous requests of the same priority level.

From high to low, interrupt sources are listed below:

IE0 TF0 IE1 TF1 RI or TI

#### **IP: INTERRUPT PRIORITY REGISTER. BIT ADDRESSABLE.**

If the bit is 0, the corresponding interrupt has a lower priority and if the bit is 1 the corresponding interrupt has a higher priority.

| -   | —    | _                                                | PS          | PT1           | PX1          | PT0         | PX0 |  |

|-----|------|--------------------------------------------------|-------------|---------------|--------------|-------------|-----|--|

| _   | IP.7 | Not implemented, reserved for future use.*       |             |               |              |             |     |  |

| _   | IP.6 | Not i                                            | mplemente   | ed, reserve   | d for future | e use.*     |     |  |

| _   | IP.5 | Not implemented, reserved for future use.*       |             |               |              |             |     |  |

| PS  | IP.4 | Defir                                            | nes the Se  | rial Port int | errupt prio  | rity level. |     |  |

| PT1 | IP.3 | Defir                                            | nes the Tin | ner 1 interr  | upt priority | level.      |     |  |

| PX1 | IP.2 | Defines External Interrupt 1 priority level.     |             |               |              |             |     |  |

| PT0 | IP.1 | Defines the Timer 0 interrupt priority level.    |             |               |              |             |     |  |

| PX0 | IP.0 | Defines the External Interrupt 0 priority level. |             |               |              |             |     |  |

\* User software should not write 1s to reserved bits. These bits may be used in future 80C51 products to invoke new features.

### TCON: TIMER/COUNTER CONTROL REGISTER. BIT ADDRESSABLE.

| TF1 | TR1                                                                                                                                                            | TF0              | TR0                                                                                                                                     | IE1           | IT1         | IE0         | IT0         |                                                |  |  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-------------|-------------|------------------------------------------------|--|--|

| TF1 | 1 TCON.7 Timer 1 overflow flag. Set by hardware when the Timer/Counter 1 overflows. Cleared by hardware as processor vectors to the interrupt service routine. |                  |                                                                                                                                         |               |             |             |             |                                                |  |  |

| TR1 | TCON.6                                                                                                                                                         | 5 Time           | er 1 run cor                                                                                                                            | ntrol bit. Se | t/cleared b | y software  | to turn Tin | ner/Counter 1 ON/OFF.                          |  |  |

| TF0 | TCON.5 Timer 0 overflow flag. Set by hardware when the Timer/Counter 0 overflows. Cleared by hardware as processor vectors to the service routine.             |                  |                                                                                                                                         |               |             |             |             |                                                |  |  |

| TR0 | TCON.4                                                                                                                                                         | Time             | Timer 0 run control bit. Set/cleared by software to turn Timer/Counter 0 ON/OFF.                                                        |               |             |             |             |                                                |  |  |

| E1  | TCON.3                                                                                                                                                         |                  | rnal Interru<br>ware when                                                                                                               |               | <b>.</b>    | •           | when Exte   | ernal Interrupt edge is detected. Cleared by   |  |  |

| T1  | TCON.2                                                                                                                                                         |                  | Interrupt 1 type control bit. Set/cleared by software to specify falling edge/low level triggered External<br>Interrupt.                |               |             |             |             |                                                |  |  |

| E0  | TCON.1                                                                                                                                                         |                  | External Interrupt 0 edge flag. Set by hardware when External Interrupt edge detected. Cleared by hardware when interrupt is processed. |               |             |             |             |                                                |  |  |

| ТО  | TCON.0                                                                                                                                                         | ) Inter<br>Inter |                                                                                                                                         | control bit   | . Set/clear | ed by softv | vare to spe | cify falling edge/low level triggered External |  |  |

#### TMOD: TIMER/COUNTER MODE CONTROL REGISTER. NOT BIT ADDRESSABLE.

| GATE    | C/T                                                                                                                                                                                                  | M1                                  | MO              | GATE         | C/T      | M1     | M0 | 7 |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------------|--------------|----------|--------|----|---|--|

|         |                                                                                                                                                                                                      |                                     |                 |              |          |        |    |   |  |

|         | Tin                                                                                                                                                                                                  | ner 1                               |                 |              | Ti       | imer 0 |    |   |  |

| GATE    | GATE When TRx (in TCON) is set and GATE = 1, TIMER/COUNTERx will run only while INTx pin is high (hardware control)<br>When GATE = 0, TIMER/COUNTERx will run only while TRx = 1 (software control). |                                     |                 |              |          |        |    |   |  |

| C/T     | Timer or Counter selector. Cleared for Timer operation (input from internal system clock). Set for Counter operation (input from Tx input pin).                                                      |                                     |                 |              |          |        |    |   |  |

| M1      | Mode s                                                                                                                                                                                               | elector b                           | it. (NOTE 1)    |              |          |        |    |   |  |

| M0      | Mode s                                                                                                                                                                                               | elector b                           | it. (NOTE 1)    |              |          |        |    |   |  |

| NOTE 1: |                                                                                                                                                                                                      |                                     |                 |              |          |        |    |   |  |

| M1      | МО                                                                                                                                                                                                   | Ореі                                | rating Mode     |              |          |        |    |   |  |

| 0       | 0                                                                                                                                                                                                    | 0                                   | 13-bit Timer (8 | 048 compat   | ible)    |        |    |   |  |

| 0       | 1                                                                                                                                                                                                    | 1                                   | 16-bit Timer/C  | ounter       |          |        |    |   |  |

| 1       | 0                                                                                                                                                                                                    | 0 2 8-bit Auto-Reload Timer/Counter |                 |              |          |        |    |   |  |

| 1       | 1 3 (Timer 0) TL0 is an 8-bit Timer/Counter controlled by the standart Timer 0 control bits. TH0 is an8-bit Timer and is controlled by Timer 1 control bits.                                         |                                     |                 |              |          |        |    |   |  |

| 1       | 1                                                                                                                                                                                                    | 3                                   | (Timer 1) Time  | er/Counter 1 | stopped. |        |    |   |  |

|         |                                                                                                                                                                                                      |                                     |                 |              |          |        |    |   |  |

#### TIMER SET-UP

Tables 2 through 5 give some values for TMOD which can be used to set up Timer 0 in different modes.

It is assumed that only one timer is being used at a time. If it is desired to run Timers 0 and 1 simultaneously, in any mode, the value in TMOD for Timer 0 must be ORed with the value shown for Timer 1 (Tables 5 and 6).

For example, if it is desired to run Timer 0 in mode 1 GATE (external control), and Timer 1 in mode 2 COUNTER, then the value that must be loaded into TMOD is 69H (09H from Table 2 ORed with 60H from Table 5).

Moreover, it is assumed that the user, at this point, is not ready to turn the timers on and will do that at a different point in the program by setting bit TRx (in TCON) to 1.

### **TIMER/COUNTER 0**

#### Table 2.As a Timer:

|      |                     | TMOD                            |                                 |  |  |  |

|------|---------------------|---------------------------------|---------------------------------|--|--|--|

| MODE | TIMER 0<br>FUNCTION | INTERNAL<br>CONTROL<br>(NOTE 1) | EXTERNAL<br>CONTROL<br>(NOTE 2) |  |  |  |

| 0    | 13-bit Timer        | 00H                             | 08H                             |  |  |  |

| 1    | 16-bit Timer        | 01H                             | 09H                             |  |  |  |

| 2    | 8-bit Auto-Reload   | 02H                             | 0AH                             |  |  |  |

| 3    | Two 8-bit Timers    | 03H                             | 0BH                             |  |  |  |

#### Table 3. As a Counter:

|      |                       | TMOD                            |                                 |  |  |  |

|------|-----------------------|---------------------------------|---------------------------------|--|--|--|

| MODE | COUNTER 0<br>FUNCTION | INTERNAL<br>CONTROL<br>(NOTE 1) | EXTERNAL<br>CONTROL<br>(NOTE 2) |  |  |  |

| 0    | 13-bit Timer          | 04H                             | 0CH                             |  |  |  |

| 1    | 16-bit Timer          | 05H                             | 0DH                             |  |  |  |

| 2    | 8-bit Auto-Reload     | 06H                             | 0EH                             |  |  |  |

| 3    | One 8-bit Counter     | 07H                             | 0FH                             |  |  |  |

NOTES:

1. The timer is turned ON/OFF by setting/clearing bit TR0 in the software.

2. The Timer is turned ON/OFF by the 1-to-0 transition on INT0 (P3.2) when TR0 = 1 (hardware control).

### **TIMER/COUNTER 1**

#### Table 4. As a Timer:

|      |                     | ТМОД                            |                                 |  |  |  |

|------|---------------------|---------------------------------|---------------------------------|--|--|--|

| MODE | TIMER 1<br>FUNCTION | INTERNAL<br>CONTROL<br>(NOTE 1) | EXTERNAL<br>CONTROL<br>(NOTE 2) |  |  |  |

| 0    | 13-bit Timer        | 00H                             | 80H                             |  |  |  |

| 1    | 16-bit Timer        | 10H                             | 90H                             |  |  |  |

| 2    | 8-bit Auto-Reload   | 20H                             | A0H                             |  |  |  |

| 3    | Does not run        | 30H                             | B0H                             |  |  |  |

#### Table 5. As a Counter:

|      |                       | ТМ                              | OD                              |

|------|-----------------------|---------------------------------|---------------------------------|

| MODE | COUNTER 1<br>FUNCTION | INTERNAL<br>CONTROL<br>(NOTE 1) | EXTERNAL<br>CONTROL<br>(NOTE 2) |

| 0    | 13-bit Timer          | 40H                             | СОН                             |

| 1    | 16-bit Timer          | 50H                             | D0H                             |

| 2    | 8-bit Auto-Reload     | 60H                             | E0H                             |

| 3    | Not available         | -                               | _                               |

NOTES:

The timer is turned ON/OFF by setting/clearing bit TR1 in the software.

The Timer is turned ON/OFF by the 1-to-0 transition on INT1 (P3.2) when TR1 = 1 (hardware control).

### SCON: SERIAL PORT CONTROL REGISTER. BIT ADDRESSABLE.

| SM0 | SM1    | SM2   | REN                                          | TB8           | RB8         | ΤI         | RI          |

|-----|--------|-------|----------------------------------------------|---------------|-------------|------------|-------------|

| SM0 | SCON.7 | Seria | al Port mod                                  | de specifie   | r. (NOTE 1) | )          |             |

| SM1 | SCON.6 | Seria | al Port mod                                  | de specifie   | r. (NOTE 1  | )          |             |

| SM2 | SCON.5 | RI w  | oles the mu<br>ill not be ad<br>ated if a va | ctivated if t | he receive  | d 9th data | bit (RB8) i |

| REN | SCON.4 | Set/0 | Cleared by                                   | software t    | o Enable/D  | isable rec | eption.     |

| TB8 | SCON.3 | The   | 9th bit that                                 | will be tra   | nsmitted in | modes 2 8  | & 3. Set/Cl |

| RB8 | SCON.2 |       | odes 2 & 3.<br>ived. In mo                   |               |             |            | ived. In mo |

| ТІ  | SCON.1 |       | smit interru<br>bit in the c                 |               | 2           |            |             |

| RI  | SCON.0 |       | eive interru<br>bit time in                  |               |             |            |             |

#### NOTE 1:

| SMO | SM1 | Mode | Description    | Baud Rate                                      |

|-----|-----|------|----------------|------------------------------------------------|

| 0   | 0   | 0    | Shift Register | F <sub>OSC.</sub> /12                          |

| 0   | 1   | 1    | 8-bit UART     | Variable                                       |

| 1   | 0   | 2    | 9-bit UART     | F <sub>OSC.</sub> /64 or F <sub>OSC.</sub> /32 |

| 1   | 1   | 3    | 9-bit UART     | Variable                                       |

### SERIAL PORT SET-UP:

#### Table 6.

| MODE             | SCON                     | SM2 VARIATION                                |

|------------------|--------------------------|----------------------------------------------|

| 0<br>1<br>2<br>3 | 10H<br>50H<br>90H<br>D0H | Single Processor<br>Environment<br>(SM2 = 0) |

| 0<br>1<br>2<br>3 | NA<br>70H<br>B0H<br>F0H  | Multiprocessor<br>Environment<br>(SM2 = 1)   |

### **GENERATING BAUD RATES**

### Serial Port in Mode 0:

Mode 0 has a fixed baud rate which is 1/12 of the oscillator frequency. To run the serial port in this mode none of the Timer/Counters need to be set up. Only the SCON register needs to be defined.

Baud Rate =

$$\frac{\text{Osc Freq}}{12}$$

### Serial Port in Mode 1:

Mode 1 has a variable baud rate. The baud rate is generated by Timer 1.

#### **USING TIMER/COUNTER 1 TO GENERATE BAUD RATES:**

For this purpose, Timer 1 is used in mode 2 (Auto-Reload). Refer to Timer Setup section of this chapter.

Baud Rate =  $\frac{K \text{ Osc Freq}}{32 \text{ 12 } [256 \text{ (TH1)}]}$

If SMOD = 0, then K = 1. If SMOD = 1, then K = 2 (SMOD is in the PCON register).

Most of the time the user knows the baud rate and needs to know the reload value for TH1.

$TH1 = 256 \qquad \frac{K \quad Osc \ Freq}{384} \quad baud \ rate$

TH1 must be an integer value. Rounding off TH1 to the nearest integer may not produce the desired baud rate. In this case, the user may have to choose another crystal frequency.

Since the PCON register is not bit addressable, one way to set the bit is logical ORing the PCON register (i.e., ORL PCON,#80H). The address of PCON is 87H.

#### SERIAL PORT IN MODE 2:

The baud rate is fixed in this mode and is 1/32 or 1/64 of the oscillator frequency, depending on the value of the SMOD bit in the PCON register.

In this mode none of the Timers are used and the clock comes from the internal phase 2 clock.

SMOD = 1, Baud Rate = 1/32 Osc Freq.

SMOD = 0, Baud Rate = 1/64 Osc Freq.

To set the SMOD bit: ORL PCON,#80H. The address of PCON is 87H.

#### **SERIAL PORT IN MODE 3:**

The baud rate in mode 3 is variable and sets up exactly the same as in mode 1.

### 80C51 FAMILY INSTRUCTION SET

### Table 7. 80C51 Instruction Set Summary

|                                                       |                                                                                                                                                                           |                                          | Interrupt Respon                                                                     | se T                            | ime: R           | efer to           | Hardware Descrip                                                                        | otion C                                             | Chapte       | er.         |                            |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------|------------------|-------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------|--------------|-------------|----------------------------|

| Instructions that Affect Flag Settings <sup>(1)</sup> |                                                                                                                                                                           |                                          |                                                                                      |                                 |                  |                   |                                                                                         |                                                     |              |             |                            |

|                                                       |                                                                                                                                                                           |                                          | Instruction                                                                          |                                 | Flag             | J                 | Instruction                                                                             |                                                     | Flag         |             |                            |

| <sup>(1)</sup> Note that                              | it operati                                                                                                                                                                | ons on SER byte a                        | ADD<br>ADDC<br>SUBB<br>MUL<br>DIV<br>DA<br>RRC<br>RLC<br>SETB C<br>ddress 208 or bit | X<br>0<br>0<br>X<br>X<br>X<br>1 | X<br>X<br>X<br>X | AC<br>X<br>X<br>X | CLR C<br>CPL C<br>ANL C,bit<br>ANL C,bit<br>ORL C,bit<br>ORL C,bit<br>MOV C,bit<br>CJNE | C<br>0<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | OV<br>in the |             | also affect flag settings. |

|                                                       |                                                                                                                                                                           |                                          |                                                                                      |                                 |                  |                   | , · ·                                                                                   |                                                     |              |             |                            |

|                                                       |                                                                                                                                                                           |                                          |                                                                                      |                                 |                  |                   | and addressing m                                                                        | odes                                                |              |             |                            |

| Rn                                                    | ot                                                                                                                                                                        | Register R7-R0 of                        |                                                                                      |                                 | 0                |                   |                                                                                         | ANA 1-                                              | ootio        | (0 107) -   | roseplio 1/0 port          |

| dire                                                  | CI                                                                                                                                                                        | 8-bit internal data control register, st |                                                                                      |                                 |                  |                   | an internal Data R                                                                      | AIVI 10                                             | catior       | 1 (0-127) 0 | r a SFR [i.e., I/O port,   |

| @R                                                    | li                                                                                                                                                                        | 8-bit internal data                      | RAM location (0                                                                      | -255                            | ) addr           | essed             | indirectly through r                                                                    | egiste                                              | er R1 (      | or R0.      |                            |

| #da                                                   | ta                                                                                                                                                                        | 8-bit constant incl                      | uded in the instru                                                                   | ictio                           | n.               |                   |                                                                                         |                                                     |              |             |                            |

|                                                       | ta 16                                                                                                                                                                     | 16-bit constant inc                      |                                                                                      |                                 |                  |                   |                                                                                         |                                                     |              |             |                            |

| add                                                   | addr 16 16-bit destination address. Used by LCALL and LJMP. A branch can be anywhere within the 64k-byte Program<br>Memory address space.                                 |                                          |                                                                                      |                                 |                  | 64k-byte Program  |                                                                                         |                                                     |              |             |                            |

| add                                                   | r 11                                                                                                                                                                      | 11-bit destination<br>program memory     |                                                                                      |                                 |                  |                   | MP. The branch wil<br>struction.                                                        | l be w                                              | ithin t      | he same 2   | k-byte page of             |

| rel                                                   | rel Signed (two's complement) 8-bit offset byte. Used by SJMP and all conditional jumps. Range is -128 to +127 bytes relative to first byte of the following instruction. |                                          |                                                                                      |                                 |                  | e is –128 to +127 |                                                                                         |                                                     |              |             |                            |

| bit                                                   |                                                                                                                                                                           | Direct Addressed                         | bit in Internal Da                                                                   | ta R                            | AM or            | Speci             | al Function Registe                                                                     | er.                                                 |              |             |                            |

|                                                       | MNE                                                                                                                                                                       | MONIC                                    |                                                                                      |                                 | DES              | CRIPT             | ION                                                                                     |                                                     | В            | YTE         | OSCILLATOR<br>PERIOD       |

| ARITHME                                               | TIC OPE                                                                                                                                                                   | RATIONS                                  |                                                                                      |                                 |                  |                   |                                                                                         |                                                     |              |             |                            |

| ADD                                                   | A,R                                                                                                                                                                       | n                                        | Add register                                                                         | to A                            | ccum             | ulator            |                                                                                         |                                                     |              | 1           | 12                         |

| ADD                                                   | A,di                                                                                                                                                                      |                                          | Add direct b                                                                         | •                               |                  |                   |                                                                                         |                                                     |              | 2           | 12                         |

| ADD                                                   | A,@                                                                                                                                                                       |                                          | Add indirect                                                                         |                                 |                  |                   |                                                                                         |                                                     |              | 1           | 12                         |

| ADD                                                   | A,#c                                                                                                                                                                      |                                          | Add immedi                                                                           |                                 |                  |                   |                                                                                         |                                                     |              | 2           | 12                         |

| ADDC                                                  | A,Ri                                                                                                                                                                      |                                          | Add register                                                                         |                                 |                  |                   | -                                                                                       |                                                     |              | 1           | 12                         |

| ADDC<br>ADDC                                          | A,di<br>A,@                                                                                                                                                               |                                          |                                                                                      | -                               |                  |                   | or with carry<br>lator with carry                                                       |                                                     |              | 2<br>1      | 12<br>12                   |

| ADDC                                                  | A,@<br>A,#c                                                                                                                                                               |                                          | Add indirect                                                                         |                                 |                  |                   | -                                                                                       |                                                     |              | 2           | 12                         |

| SUBB                                                  | A,R                                                                                                                                                                       |                                          | Subtract Re                                                                          |                                 |                  |                   | •                                                                                       |                                                     |              | 1           | 12                         |

| SUBB                                                  | A,di                                                                                                                                                                      |                                          |                                                                                      |                                 |                  |                   | with borrow                                                                             |                                                     |              | 2           | 12                         |

| SUBB                                                  | A,@                                                                                                                                                                       |                                          |                                                                                      |                                 |                  |                   | ACC with borrow                                                                         |                                                     |              | 1           | 12                         |

| SUBB                                                  | A,#c                                                                                                                                                                      |                                          |                                                                                      |                                 |                  |                   | n A <sub>CC</sub> with borrow                                                           |                                                     |              | 2           | 12                         |

| INC                                                   | А                                                                                                                                                                         |                                          | Increment A                                                                          | ccur                            | nulato           | r                 |                                                                                         |                                                     |              | 1           | 12                         |

|                                                       |                                                                                                                                                                           |                                          |                                                                                      |                                 |                  |                   |                                                                                         |                                                     |              |             |                            |

All mnemonics copyrighted © Intel Corporation 1980

12

1

INC

Rn

Increment register

|         | MNEMONIC            | DESCRIPTION                                | BYTE | OSCILLATOR<br>PERIOD |

|---------|---------------------|--------------------------------------------|------|----------------------|

| ARITHME | TIC OPERATIONS (Cor | ntinued)                                   |      |                      |

| INC     | direct              | Increment direct byte                      | 2    | 12                   |

| INC     | @Ri                 | Increment indirect RAM                     | 1    | 12                   |

| DEC     | А                   | Decrement Accumulator                      | 1    | 12                   |

| DEC     | Rn                  | Decrement Register                         | 1    | 12                   |

| DEC     | direct              | Decrement direct byte                      | 2    | 12                   |

| DEC     | @Ri                 | Decrement indirect RAM                     | 1    | 12                   |

| INC     | DPTR                | Increment Data Pointer                     | 1    | 24                   |

| MUL     | AB                  | Multiply A and B                           | 1    | 48                   |

| DIV     | AB                  | Divide A by B                              | 1    | 48                   |

| DA      | А                   | Decimal Adjust Accumulator                 | 1    | 12                   |

|         | OPERATIONS          |                                            |      |                      |

| ANL     | A,Rn                | AND Register to Accumulator                | 1    | 12                   |

| ANL     | A,direct            | AND direct byte to Accumulator             | 2    | 12                   |

| ANL     | A,@Ri               | AND indirect RAM to Accumulator            | 1    | 12                   |

| ANL     | A,#data             | AND immediate data to Accumulator          | 2    | 12                   |

| ANL     | direct,A            | AND Accumulator to direct byte             | 2    | 12                   |

| ANL     | direct,#data        | AND immediate data to direct byte          | 3    | 24                   |

| ORL     | A,Rn                | OR register to Accumulator                 | 1    | 12                   |

| ORL     | A, direct           | OR direct byte to Accumulator              | 2    | 12                   |

| ORL     | A,@Ri               | OR indirect RAM to Accumulator             | 1    | 12                   |

| ORL     | A,#data             | OR immediate data to Accumulator           | 2    | 12                   |

| ORL     | direct,A            | OR Accumulator to direct byte              | 2    | 12                   |

| ORL     | direct,#data        | OR immediate data to direct byte           | 3    | 24                   |

| XRL     | A,Rn                | Exclusive-OR register to Accumulator       | 1    | 12                   |

| XRL     | A,direct            | Exclusive-OR direct byte to Accumulator    | 2    | 12                   |

| XRL     | A,@Ri               | Exclusive-OR indirect RAM to Accumulator   | 1    | 12                   |

| XRL     | A,#data             | Exclusive-OR immediate data to Accumulator | 2    | 12                   |

| XRL     | direct,A            | Exclusive-OR Accumulator to direct byte    | 2    | 12                   |

| XRL     | direct,#data        | Exclusive-OR immediate data to direct byte | 3    | 24                   |

| CLR     | А                   | Clear Accumulator                          | 1    | 12                   |

| CPL     | А                   | Complement Accumulator                     | 1    | 12                   |

| RL      | А                   | Rotate Accumulator left                    | 1    | 12                   |

| RLC     | А                   | Rotate Accumulator left through the carry  | 1    | 12                   |

| RR      | А                   | Rotate Accumulator right                   | 1    | 12                   |

| RRC     | А                   | Rotate Accumulator right through the carry | 1    | 12                   |

| SWAP    | А                   | Swap nibbles within the Accumulator        | 1    | 12                   |

| DATA TR | ANSFER              |                                            |      |                      |

| MOV     | A,Rn                | Move register to Accumulator               | 1    | 12                   |

| MOV     | A,direct            | Move direct byte to Accumulator            | 2    | 12                   |

| MOV     | A,@Ri               | Move indirect RAM to Accumulator           | 1    | 12                   |

### Table 7. 80C51 Instruction Set Summary (Continued)

All mnemonics copyrighted © Intel Corporation 1980

|          | MNEMONIC          | DESCRIPTION                                         | BYTE | OSCILLATOR<br>PERIOD |

|----------|-------------------|-----------------------------------------------------|------|----------------------|

| DATA TRA | NSFER (Continued) |                                                     |      |                      |

| MOV      | A,#data           | Move immediate data to Accumulator                  | 2    | 12                   |

| MOV      | Rn,A              | Move Accumulator to register                        | 1    | 12                   |

| MOV      | Rn,direct         | Move direct byte to register                        | 2    | 24                   |

| MOV      | RN,#data          | Move immediate data to register                     | 2    | 12                   |

| MOV      | direct,A          | Move Accumulator to direct byte                     | 2    | 12                   |

| MOV      | direct,Rn         | Move register to direct byte                        | 2    | 24                   |

| MOV      | direct, direct    | Move direct byte to direct                          | 3    | 24                   |

| MOV      | direct,@Ri        | Move indirect RAM to direct byte                    | 2    | 24                   |

| MOV      | direct,#data      | Move immediate data to direct byte                  | 3    | 24                   |

| MOV      | @Ri,A             | Move Accumulator to indirect RAM                    | 1    | 12                   |

| MOV      | @Ri,direct        | Move direct byte to indirect RAM                    | 2    | 24                   |

| MOV      | @Ri,#data         | Move immediate data to indirect RAM                 | 2    | 12                   |

| MOV      | DPTR,#data16      | Load Data Pointer with a 16-bit constant            | 3    | 24                   |

| MOVC     | A,@A+DPTR         | Move Code byte relative to DPTR to $A_{CC}$         | 1    | 24                   |

| MOVC     | A,@A+PC           | Move Code byte relative to PC to A <sub>CC</sub>    | 1    | 24                   |

| MOVX     | A,@Ri             | Move external RAM (8-bit addr) to A <sub>CC</sub>   | 1    | 24                   |

| MOVX     | A,@DPTR           | Move external RAM (16-bit addr) to $A_{CC}$         | 1    | 24                   |

| MOVX     | A,@Ri,A           | Move A <sub>CC</sub> to external RAM (8-bit addr)   | 1    | 24                   |

| MOVX     | @DPTR,A           | Move A <sub>CC</sub> to external RAM (16-bit addr)  | 1    | 24                   |

| PUSH     | direct            | Push direct byte onto stack                         | 2    | 24                   |

| POP      | direct            | Pop direct byte from stack                          | 2    | 24                   |

| ХСН      | A,Rn              | Exchange register with Accumulator                  | 1    | 12                   |

| ХСН      | A,direct          | Exchange direct byte with Accumulator               | 2    | 12                   |

| ХСН      | A,@Ri             | Exchange indirect RAM with Accumulator              | 1    | 12                   |

| XCHD     | A,@Ri             | Exchange low-order digit indirect RAM with $A_{CC}$ | 1    | 12                   |

| BOOLEAN  | VARIABLE MANIPULA | TION                                                |      |                      |

| CLR      | С                 | Clear carry                                         | 1    | 12                   |

| CLR      | bit               | Clear direct bit                                    | 2    | 12                   |

| SETB     | С                 | Set carry                                           | 1    | 12                   |

| SETB     | bit               | Set direct bit                                      | 2    | 12                   |

| CPL      | С                 | Complement carry                                    | 1    | 12                   |

| CPL      | bit               | Complement direct bit                               | 2    | 12                   |

| ANL      | C,bit             | AND direct bit to carry                             | 2    | 24                   |

| ANL      | C,/bit            | AND complement of direct bit to carry               | 2    | 24                   |

| ORL      | C,bit             | OR direct bit to carry                              | 2    | 24                   |

| ORL      | C,/bit            | OR complement of direct bit to carry                | 2    | 24                   |

| MOV      | C,bit             | Move direct bit to carry                            | 2    | 12                   |

| MOV      | bit,C             | Move carry to direct bit                            | 2    | 24                   |

| JC       | rel               | Jump if carry is set                                | 2    | 24                   |

| JNC      | rel               | Jump if carry not set                               | 2    | 24                   |

#### Table 7. 80C51 Instruction Set Summary (Continued)

All mnemonics copyrighted © Intel Corporation 1980

|         | MNEMONIC          | DESCRIPTION                                                  | BYTE | OSCILLATOR<br>PERIOD |

|---------|-------------------|--------------------------------------------------------------|------|----------------------|

| BOOLEAN | VARIABLE MANIPULA | TION (Continued)                                             |      |                      |

| JB      | rel               | Jump if direct bit is set                                    | 3    | 24                   |

| JNB     | rel               | Jump if direct bit is not set                                | 3    | 24                   |

| JBC     | bit,rel           | Jump if direct bit is set and clear bit                      | 3    | 24                   |

| PROGRAM | BRANCHING         |                                                              |      |                      |

| ACALL   | addr11            | Absolute subroutine call                                     | 2    | 24                   |

| LCALL   | addr16            | Long subroutine call                                         | 3    | 24                   |

| RET     |                   | Return from subroutine                                       | 1    | 24                   |

| RETI    |                   | Return from interrupt                                        | 1    | 24                   |

| AJMP    | addr11            | Absolute jump                                                | 2    | 24                   |

| LJMP    | addr16            | Long jump                                                    | 3    | 24                   |

| SJMP    | rel               | Short jump (relative addr)                                   | 2    | 24                   |

| JMP     | @A+DPTR           | Jump indirect relative to the DPTR                           | 1    | 24                   |

| JZ      | rel               | Jump if Accumulator is zero                                  | 2    | 24                   |

| JNZ     | rel               | Jump if Accumulator is not zero                              | 2    | 24                   |

| CJNE    | A,direct,rel      | Compare direct byte to A <sub>CC</sub> and jump if not equal | 3    | 24                   |

| CJNE    | A,#data,rel       | Compare immediate to A <sub>CC</sub> and jump if not equal   | 3    | 24                   |

| CJNE    | RN,#data,rel      | Compare immediate to register and jump if not equal          | 3    | 24                   |

| CJNE    | @Ri,#data,rel     | Compare immediate to indirect and jump if not equal          | 3    | 24                   |

| DJNZ    | Rn,rel            | Decrement register and jump if not zero                      | 2    | 24                   |

| DJNZ    | direct,rel        | Decrement direct byte and jump if not zero                   | 3    | 24                   |

| NOP     |                   | No operation                                                 | 1    | 12                   |

### Table 7. 80C51 Instruction Set Summary (Continued)

All mnemonics copyrighted © Intel Corporation 1980

### INSTRUCTION DEFINITIONS

#### ACALL addr11

| Function:    | Absolute Call                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description: | ACALL unconditionally calls a subroutine located at the indicated address. The instruction increments the PC twice to obtain the address of the following instruction, then pushes the 16-bit result onto the stack (low-order byte first) and increments the Stack Pointer twice. The destination address is obtained by successively concatenating the five high-order bits of the incremented PC, opcode bits 7-5, and the second byte of the instruction. The subroutine called must therefore start within the same 2k block of the program memory as the first byte of the instruction following ACALL. No flags are affected. |

| Example:     | Initially SP equals 07H. The label "SUBRTN" is at program memory location 0345 H. After executing the instruction,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              | ACALL SUBRTN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | at location 0123H, SP will contain 09H, internal RAM locations 08H and 09H will contain 25H and 01H, respectively, and the PC will contain 0345H.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Bytes:       | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Cycles:      | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Encoding:    | a10a9 a8 1 0 0 0 1 a7 a6 a5 a4 a3 a2 a1 a0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Operation:   | $\begin{array}{l} ACALL \\ (PC) \leftarrow (PC) + 2 \\ (SP) \leftarrow (SP) + 1 \\ (SP) \leftarrow (PC_{7\text{-}0}) \\ (SP) \leftarrow (SP) + 1 \\ (SP) \leftarrow (PC_{15\text{-}8}) \\ (PC_{10\text{-}0}) \leftarrow page \ address \end{array}$                                                                                                                                                                                                                                                                                                                                                                                  |

## ADD A,<src-byte>

| ADD A, <src-by< th=""><th>rte&gt;</th></src-by<> | rte>                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function:                                        | Add                                                                                                                                                                                                                                                                                                          |

| Description:                                     | ADD adds the byte variable indicated to the Accumulator, leaving the result in the Accumulator. The carry and auxiliary-carry flags are set, respectively, if there is a carry-out from bit 7 or bit 3, and cleared otherwise. When adding unsigned integers, the carry flag indicates an overflow occurred. |

|                                                  | OV is set if there is a carry-out of bit 6 but not out of bit 7, or a carry-out of bit 7 but not bit 6; otherwise OV is cleared. When adding signed integers, OV indicates a negative number produced as the sum of two positive operands, or a positive sum from two negative operands.                     |

|                                                  | Four source operand addressing modes are allowed: register, direct, register-indirect, or immediate.                                                                                                                                                                                                         |

| Example:                                         | The Accumulator holds 0C3H (11000011B) and register 0 holds 0AAH (10101010B). The instruction, ADD A,R0                                                                                                                                                                                                      |

|                                                  | will leave 6DH (01101101B) in the Accumulator with the AC flag cleared and both the Carry flag and OV set to 1.                                                                                                                                                                                              |

| ADD A,Rn                                         |                                                                                                                                                                                                                                                                                                              |

| Bytes:                                           | 1                                                                                                                                                                                                                                                                                                            |