# Quartus II Version 6.0 Handbook Volume 4: SOPC Builder

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com

Copyright © 2006 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in

formation and before placing orders for products or services.

I.S. EN ISO 9001

ii Altera Corporation

# **Contents**

| Chapter Revision Dates                             | xi          |

|----------------------------------------------------|-------------|

| About this Handbook                                | xiii        |

| How to Contact Altera                              | xiii        |

| Typographic Conventions                            | xiv         |

| Section I. SOPC Builder Features                   |             |

| Revision History                                   | Section I–1 |

| Chapter 1. Introduction to SOPC Builder            |             |

| Overview                                           | 1_1         |

| Architecture of SOPC Builder Systems               |             |

| SOPC Builder Components                            |             |

| SOPC Builder Ready Components                      |             |

| User-Defined Components                            |             |

| Avalon Switch Fabric                               |             |

| Functions of SOPC Builder                          |             |

| Defining & Generating the System Hardware          | 1–5         |

| Creating a Memory Map for Software Development     |             |

| Creating a Simulation Model & Testbench            |             |

| Getting Started                                    | 1–7         |

| Chapter 2. Tour of the SOPC Builder User Interface |             |

| Starting SOPC Builder                              | 2–1         |

| Starting a New SOPC Builder System                 |             |

| Working with SOPC Builder Systems                  |             |

| System Contents Tab                                |             |

| Adding a Component to the System                   | 2–5         |

| Specifying Connections, Base Address, Clock & IRQ  |             |

| Connection Panel                                   |             |

| Table of Active Components                         | 2–7         |

| Creating User-Defined Components                   | 2–7         |

| System Dependency Tabs                             | 2–8         |

| Roard Settings Tah                                 | 2.0         |

Altera Corporation iii

| System Generation Tab                                       | 2–10 |

|-------------------------------------------------------------|------|

| System Generation Tab Options                               |      |

| SDK Option                                                  |      |

| HDL Option                                                  |      |

| Simulation Option                                           |      |

| Starting System Generation                                  |      |

| Other Tools                                                 |      |

| Preferences                                                 |      |

|                                                             |      |

| Chapter 3. Avalon Switch Fabric                             |      |

| Introduction                                                | 3–1  |

| High-Level Description                                      |      |

| Fundamentals of Avalon Switch Fabric Implementation         |      |

| Functions of Avalon Switch Fabric                           |      |

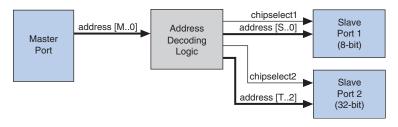

| Address Decoding                                            |      |

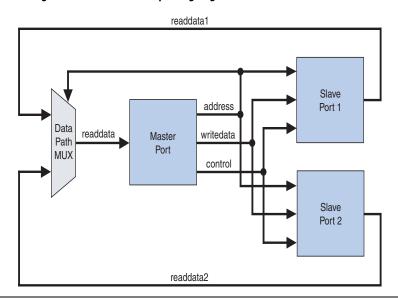

| Data-Path Multiplexing                                      |      |

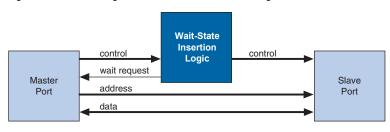

| Wait-State Insertion                                        |      |

| Pipelining for High Performance                             |      |

| Pipeline Management                                         |      |

| Endian Conversion                                           |      |

| Native Address Alignment & Dynamic Bus Sizing               |      |

| Native Address Alignment                                    |      |

| Dynamic Bus Sizing                                          | 3–11 |

| Wider Master                                                |      |

| Narrower Master                                             |      |

| Arbitration for Multi-Master Systems                        |      |

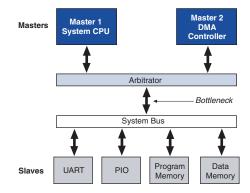

| Traditional Shared Bus Architectures                        |      |

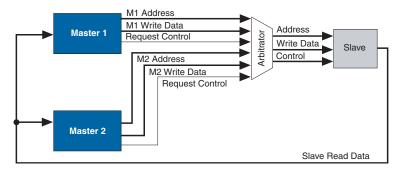

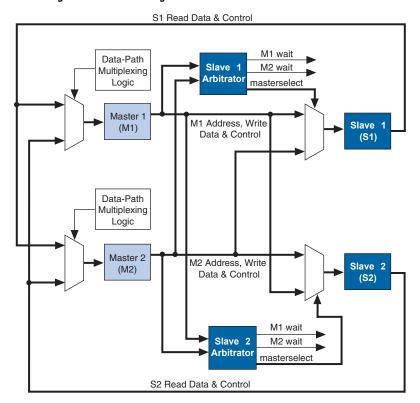

| Slave-Side Arbitration                                      |      |

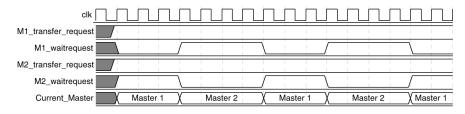

| Arbitrator Details                                          |      |

| Arbitration Rules                                           |      |

| Fairness-Based Shares                                       |      |

| Round-Robin Scheduling                                      |      |

| Burst Transfers                                             |      |

| Minimum Share Value                                         |      |

| Setting Arbitration Parameters in the SOPC Builder GUI      | 3–20 |

| Burst Management                                            |      |

| Clock Domain Crossing                                       | 3–21 |

| Description of Clock Domain-Crossing Logic                  | 3–21 |

| Location of Clock Domain Crossing Logic                     |      |

| Duration of Transfers Crossing Clock Domains                |      |

| Implementing Multiple Clock Domains in the SOPC Builder GUI | 3–24 |

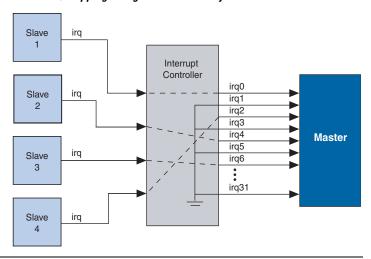

| Interrupt Controller                                        |      |

| Software Priority                                           |      |

| Hardware Priority                                           |      |

| Assigning IRQs in the SOPC Builder GUI                      |      |

| Reset Distribution                                          |      |

|                                                             |      |

| Chapter 4. SOPC Builder Components                           |      |

|--------------------------------------------------------------|------|

| Introduction                                                 | 4–1  |

| Sources of Components                                        | 4–1  |

| Location of the Component Hardware                           | 4–2  |

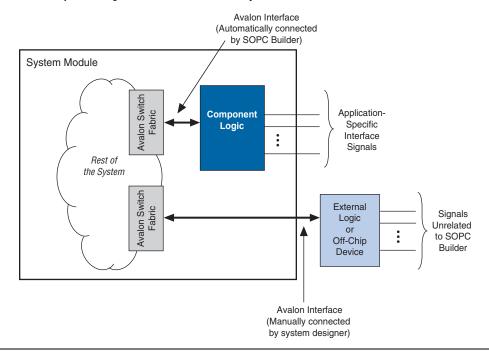

| Components That Include Logic Inside the System Module       | 4–2  |

| Components That Interface to Logic Outside the System Module | 4–3  |

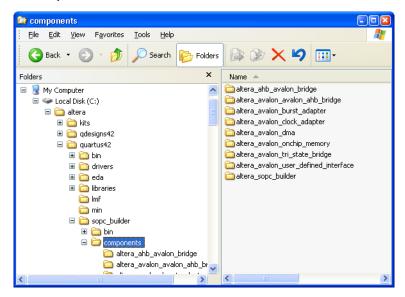

| Structure & Contents of a Component Directory                |      |

| class.ptf File                                               |      |

| cb_generator.pl File                                         | 4-4  |

| hdl Directory                                                |      |

| Other Component Files                                        | 4-!  |

| Component Directory Location                                 |      |

| Chapter 5. Component Editor                                  |      |

| Introduction                                                 | 5–7  |

| Component Editor Output                                      |      |

| Starting the Component Editor                                | 5–3  |

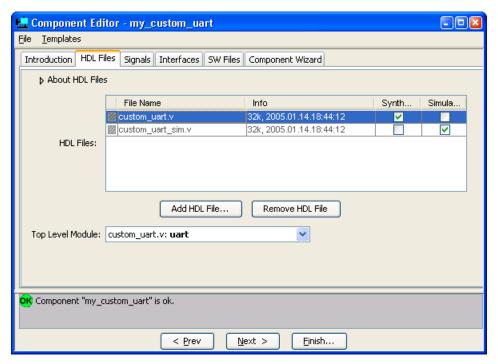

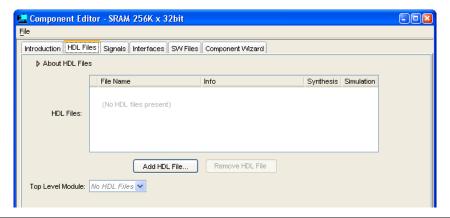

| HDL Files Tab                                                | 5–3  |

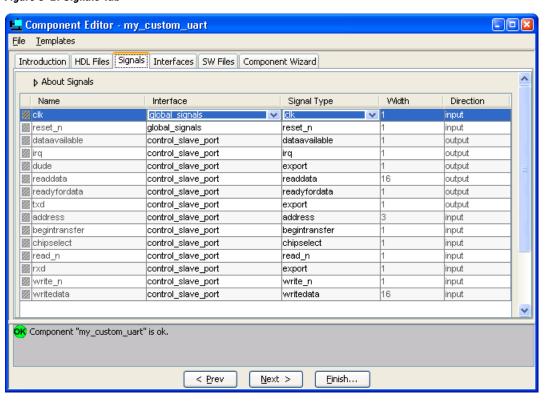

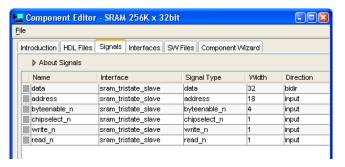

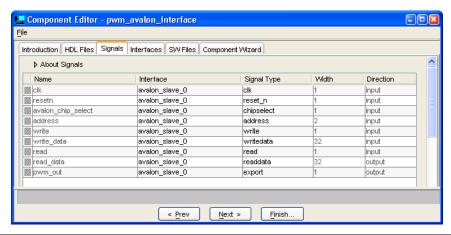

| Signals Tab                                                  | 5–:  |

| Naming Signals for Automatic Type and Interface Recognition  | 5–6  |

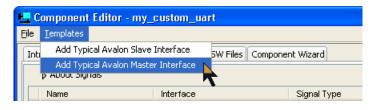

| Templates for Interfaces to External Logic                   | 5–7  |

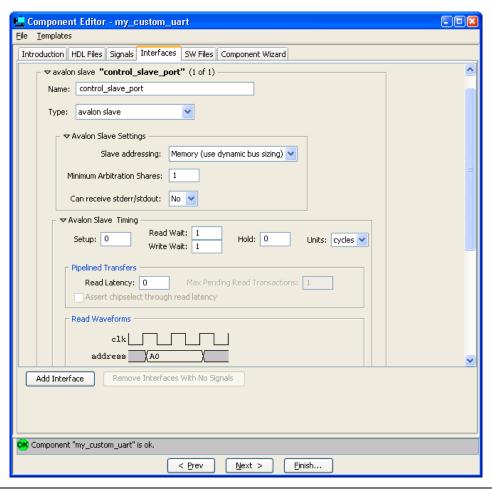

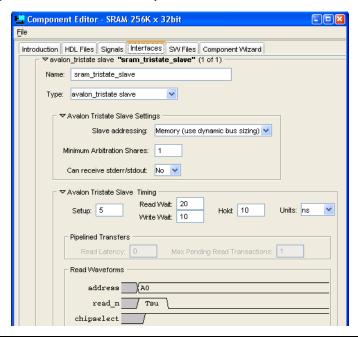

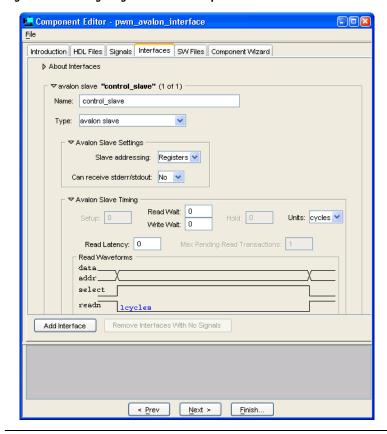

| Interfaces Tab                                               | 5–7  |

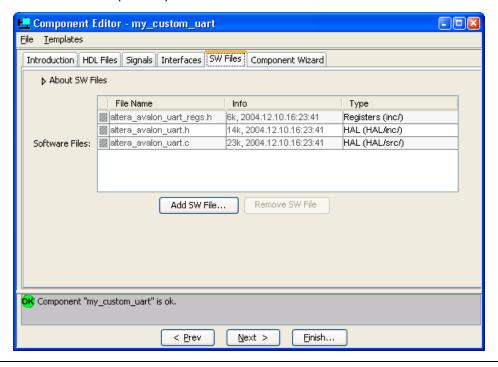

| SW Files Tab                                                 | 5–9  |

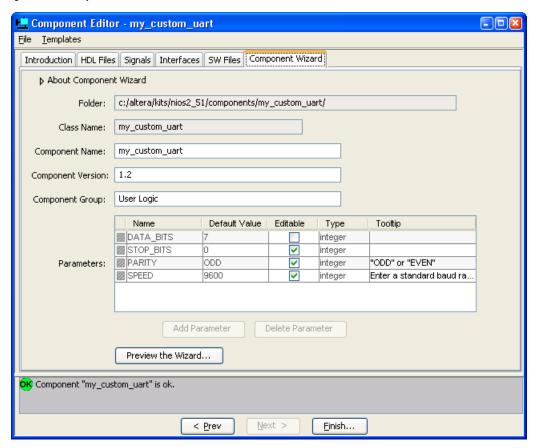

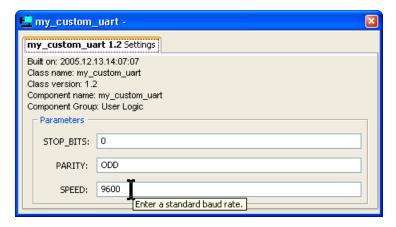

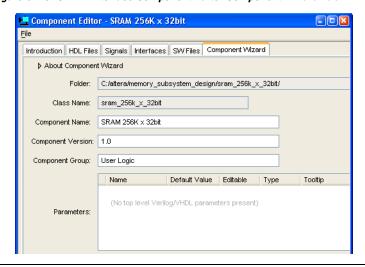

| Component Wizard Tab                                         | 5–10 |

| Identifying Information                                      | 5–10 |

| Parameters                                                   | 5–13 |

| Saving a Component                                           | 5–12 |

| Re-Editing a Component                                       | 5–13 |

| Chapter 6. Archiving SOPC Builder Projects                   |      |

| Introduction                                                 |      |

| Scope                                                        |      |

| Required Files                                               |      |

| SOPC Builder Design Files                                    | 6–2  |

| Nios II Application Software Project Files                   | 6–3  |

| Nios II System Library Project                               |      |

| File Write Permissions                                       | 6–4  |

| Chapter 7. Board Description Editor                          |      |

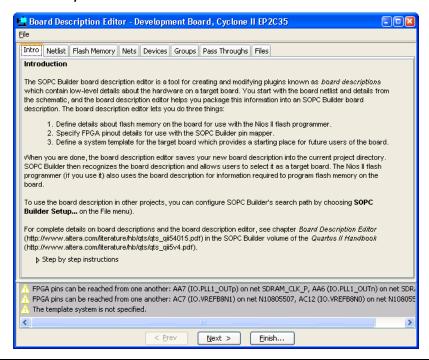

| Introduction                                                 |      |

| Board Descriptions                                           | 7–1  |

| Uses for Board Descriptions                                  |      |

| Board Description Editor                                     | 7–2  |

| Creating a Board Description                                 | 7_   |

Altera Corporation

| Pins Flow                                          | 7–4  |

|----------------------------------------------------|------|

| Steps for the Pins Flow                            | 7–5  |

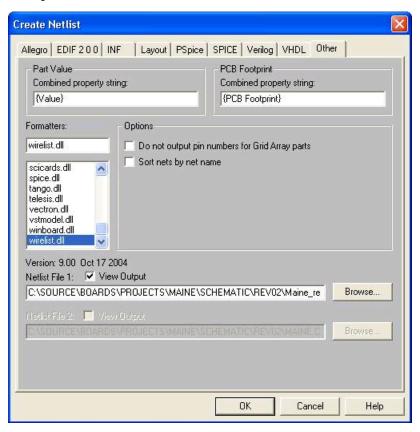

| Creating a PCB Model from the Netlist              |      |

| Flash Flow                                         | 7–8  |

| Board Description Editor Output                    |      |

| Board Description File Structure                   |      |

| Using Board Descriptions                           |      |

| Starting the Board Description Editor              |      |

| Intro Tab                                          |      |

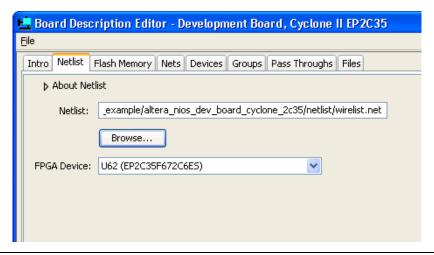

| Netlist Tab                                        |      |

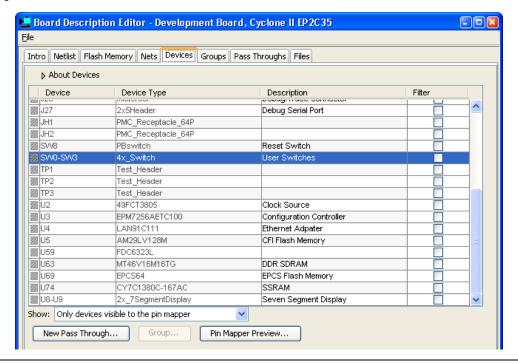

| Devices Tab                                        |      |

| Device List                                        | 7–12 |

| Filtered Nets, Pass Throughs & Device Groups       | 7–13 |

| Creating Pass Throughs                             |      |

| Creating Device Groups                             | 7–14 |

| Filtering False Target Devices                     | 7–15 |

| Previewing Pins Visible to the Pin Mapper          |      |

| Nets Tab                                           |      |

| Pass Throughs Tab                                  | 7–18 |

| Groups Tab                                         | 7–20 |

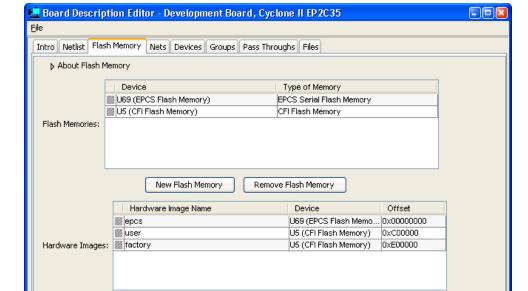

| Flash Memory Tab                                   | 7–21 |

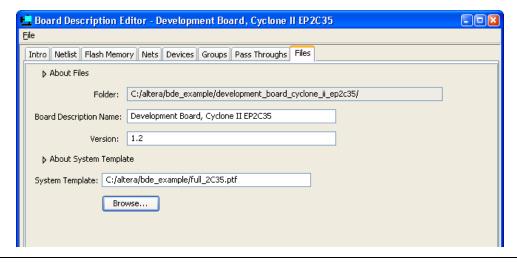

| Files Tab                                          | 7–22 |

| Board Description Name and Version                 | 7–23 |

| System Template                                    | 7–23 |

| Saving & Exiting the Board Description Editor      | 7–24 |

| Chapter 8. Pin Mapper                              |      |

| Introduction                                       | Q 1  |

| Design Flow                                        |      |

| Applying Pin Assignments to the Quartus II Project |      |

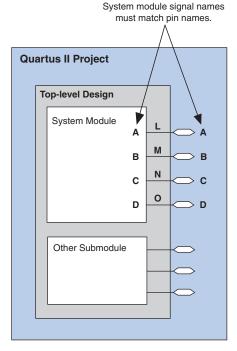

| Pin Name Requirements                              |      |

| Pin Mapper GUI                                     |      |

| Source Signals Column                              |      |

| Target Device Column                               |      |

| Target Pin Column                                  |      |

| Vector Signals                                     |      |

| Differential Signals                               |      |

| Signals with Multiple Destinations                 |      |

| Assign in Quartus II                               |      |

| Pin Mappings Status                                |      |

|                                                    |      |

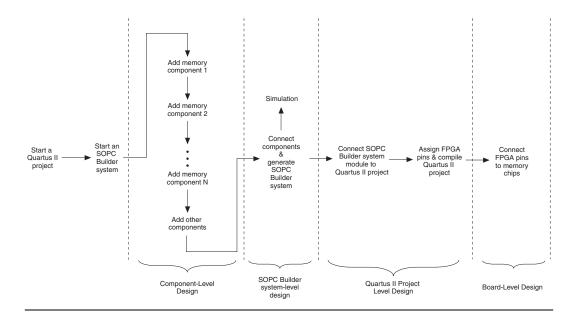

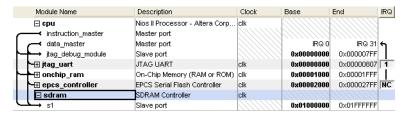

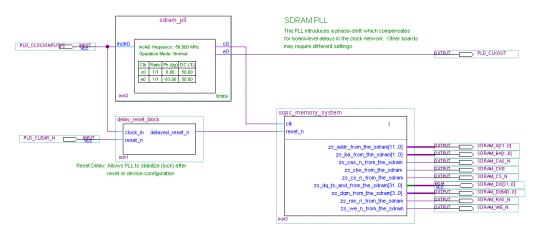

### Section II. Building Systems with SOPC Builder Revision History ...... Section II-1 Chapter 9. Building Memory Subsystems Using SOPC Builder Example Design 9–2 Design Flow 9-5 Simulation 9–7 Simulation Considerations 9–7 On-Chip RAM & ROM .......9-9 Component-Level Design for On-Chip Memory .......9–9 Read Latency 9–10 EPCS Serial Configuration Device 9–13 SOPC Builder System-Level Design for SDRAM .......9-16 Accommodating Clock Skew 9–17 Example Design with SDRAM 9–18

Altera Corporation vii

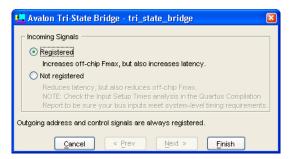

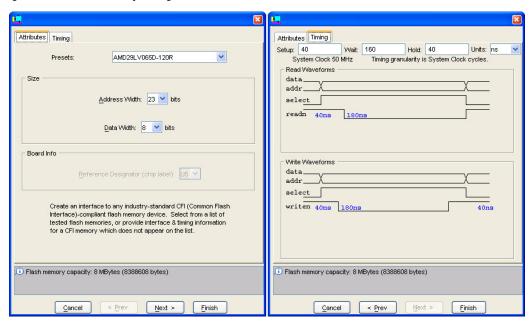

| Off-Chip SRAM & Flash Memory                             | 9–21  |

|----------------------------------------------------------|-------|

| Component-Level Design for SRAM & Flash Memory           | 9–21  |

| Avalon Tristate Bridge                                   |       |

| Flash Memory                                             | 9–23  |

| SRAM                                                     | 9–23  |

| SOPC Builder System-Level Design for SRAM & Flash Memory | 9–24  |

| Simulation for SRAM & Flash Memory                       |       |

| Quartus II Project-Level Design for SRAM & Flash Memory  | 9–25  |

| Board-Level Design for SRAM & Flash Memory               |       |

| Aligning the Least-Significant Address Bits              |       |

| Aligning the Most-Significant Address Bits               | 9–26  |

| Example Design with SRAM & Flash Memory                  | 9–26  |

| Adding the Avalon Tristate Bridge                        |       |

| Adding the Flash Memory Interface                        |       |

| Adding the SRAM Interface                                | 9–28  |

| SOPC Builder System Contents Tab                         | 9–31  |

| Connecting & Assigning Pins in the Quartus II Project    | 9–31  |

| Connecting FPGA Pins to Devices on the Board             | 9–32  |

|                                                          |       |

| Chapter 10. Developing Components for SOPC Builder       |       |

| Introduction                                             | 10–1  |

| SOPC Builder Components & the Component Editor           | 10–1  |

| Assumptions About the Reader                             | 10–2  |

| Hardware & Software Requirements                         | 10–2  |

| Component Development Flow                               | 10–3  |

| Typical Design Steps                                     |       |

| Hardware Design                                          | 10–4  |

| Software Design                                          |       |

| Verifying the Component                                  | 10–7  |

| Unit Verification                                        | 10–7  |

| System-Level Verification                                | 10–7  |

| Design Example: Pulse-Width Modulator Slave              | 10–8  |

| Install the Design Files                                 | 10–8  |

| Review the Example Design Specifications                 | 10–9  |

| PWM Design Files                                         | 10–10 |

| Functional Specification                                 | 10–10 |

| PWM Task Logic                                           | 10–11 |

| Register File                                            |       |

| Avalon Interface                                         | 10–13 |

| Software API                                             | 10–14 |

| Package the Design Files into an SOPC Builder Component  | 10–15 |

| Open the Quartus II Project & Start the Component Editor |       |

| HDL Files Tab                                            |       |

| Signals Tab                                              |       |

| Interfaces Tab                                           |       |

| Software Files (SW Files) Tab                            |       |

| Component Wizard Tab                                     |       |

|                                                          |       |

| Save the Component                                         |       |

|------------------------------------------------------------|-------|

| Instantiate the Component in Hardware                      |       |

| Add a PWM Component to the SOPC Builder System             | 10–22 |

| Modify the Quartus II Design to Use the PWM Output         | 10–23 |

| Compile the Hardware Design & Download to the Target Board | 10–24 |

| Exercise the Hardware Using Nios II Software               | 10–24 |

| Start the Nios II IDE & Create a New IDE Project           | 10–25 |

| Compile the Software Project & Run on the Target Board     |       |

| Sharing Components                                         | 10–28 |

|                                                            |       |

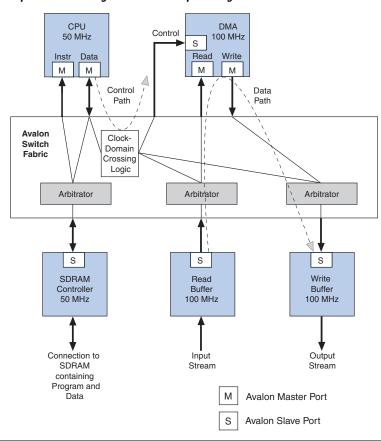

| Chapter 11. Building Systems with Multiple Clock Domains   |       |

| Introduction                                               |       |

| Example Design Overview                                    | 11–1  |

| Hardware & Software Requirements                           | 11–2  |

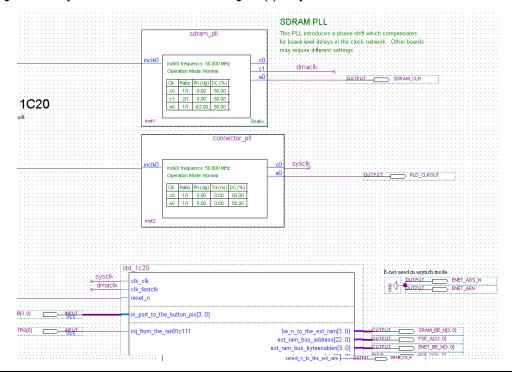

| Creating the Multi-Clock Hardware System                   | 11–3  |

| Copy the Hardware Design Files to a New Directory          | 11–4  |

| Modify the Design in SOPC Builder                          | 11–4  |

| Open the System in SOPC Builder                            | 11–5  |

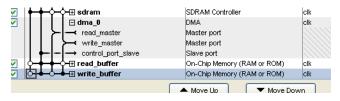

| Add DMA Controller & Memory Components                     |       |

| Connect DMA Master Ports to Memory Slave Ports             | 11–6  |

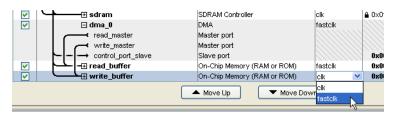

| Make Clock Domain Assignments                              | 11–7  |

| Update the Quartus II Design                               | 11–8  |

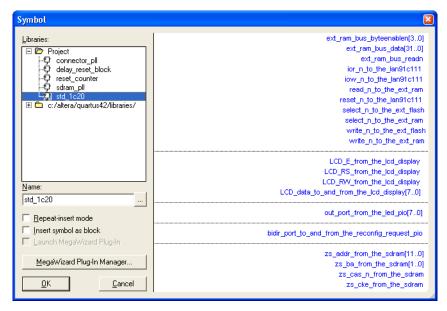

| Update the System Module Symbol                            |       |

| Update PLL Settings to Generate a 100 MHz Clock            |       |

| Connect the 100 MHz Clock to the System Module             | 11–12 |

| Compile the Design & Download to the Board                 | 11–14 |

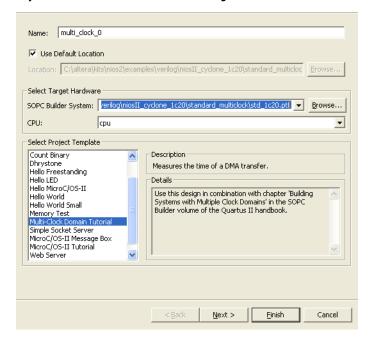

| Running Software to Exercise the Multi-Clock Hardware      | 11–15 |

| Install the Example Software Design Files                  | 11–16 |

| Create a New Nios II IDE Project                           | 11–16 |

| Build & Run the Program                                    | 11–18 |

| Conclusion                                                 | 11 10 |

Altera Corporation ix

x Altera Corporation

# **Chapter Revision Dates**

The chapters in this book, *Quartus II Handbook, Volume 4*, were revised on the following dates. Where chapters or groups of chapters are available separately, part numbers are listed.

Chapter 1. Introduction to SOPC Builder

Revised: May 2006 Part number: QII54001-6.0.0

Chapter 2. Tour of the SOPC Builder User Interface

Revised: May 2006 Part number: QII54002-6.0.0

Chapter 3. Avalon Switch Fabric

Revised: May 2006 Part number: QII54003-6.0.0

Chapter 4. SOPC Builder Components

Revised: May 2006 Part number: QII54004-6.0.0

Chapter 5. Component Editor

Revised: May 2006 Part number: QII54005-6.0.0

Chapter 6. Archiving SOPC Builder Projects

Revised: May 2006 Part number: QII54017-6.0.0

Chapter 7. Board Description Editor

Revised: May 2006 Part number: QII54017-6.0.0

Chapter 8. Pin Mapper

Revised: May 2006 Part number: QII54016-6.0.0

Chapter 9. Building Memory Subsystems Using SOPC Builder

Revised: *May* 2006 Part number: *QII54006-6.0.0*

Altera Corporation xi

Chapter 10. Developing Components for SOPC Builder

Revised: May 2006 Part number: QII54007-6.0.0

Chapter 11. Building Systems with Multiple Clock Domains

Revised: May 2006 Part number: QII54008-6.0.0

xii Altera Corporation

# **About this Handbook**

This handbook provides comprehensive information about the Altera® SOPC Builder tool.

# How to Contact Altera

For the most up-to-date information about Altera products, go to the Altera world-wide web site at www.altera.com. For technical support on this product, go to www.altera.com/mysupport. For additional information about Altera products, consult the sources shown below.

| Information Type               | USA & Canada                                                   | All Other Locations                                                    |

|--------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|

| Technical support              | www.altera.com/mysupport/                                      | www.altera.com/mysupport/                                              |

|                                | (800) 800-EPLD (3753)<br>(7:00 a.m. to 5:00 p.m. Pacific Time) | +1 408-544-8767<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time  |

| Product literature             | www.altera.com                                                 | www.altera.com                                                         |

| Altera literature services     | literature@altera.com                                          | literature@altera.com                                                  |

| Non-technical customer service | (800) 767-3753                                                 | + 1 408-544-7000<br>7:00 a.m. to 5:00 p.m. (GMT -8:00)<br>Pacific Time |

| FTP site                       | ftp.altera.com                                                 | ftp.altera.com                                                         |

Altera Corporation xiii

# Typographic Conventions

This document uses the typographic conventions shown below.

| Visual Cue                                  | Meaning                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bold Type with Initial<br>Capital Letters   | Command names, dialog box titles, checkbox options, and dialog box options are shown in bold, initial capital letters. Example: <b>Save As</b> dialog box.                                                                                                                                                              |

| bold type                                   | External timing parameters, directory names, project names, disk drive names, filenames, filename extensions, and software utility names are shown in bold type. Examples: f <sub>MAX</sub> , \qdesigns directory, d: drive, chiptrip.gdf file.                                                                         |

| Italic Type with Initial Capital<br>Letters | Document titles are shown in italic type with initial capital letters. Example: AN 75: High-Speed Board Design.                                                                                                                                                                                                         |

| Italic type                                 | Internal timing parameters and variables are shown in italic type. Examples: $t_{PlA}$ , $n+1$ .                                                                                                                                                                                                                        |

|                                             | Variable names are enclosed in angle brackets (< >) and shown in italic type. Example: <file name="">, <project name="">.pof file.</project></file>                                                                                                                                                                     |

| Initial Capital Letters                     | Keyboard keys and menu names are shown with initial capital letters. Examples: Delete key, the Options menu.                                                                                                                                                                                                            |

| "Subheading Title"                          | References to sections within a document and titles of on-line help topics are shown in quotation marks. Example: "Typographic Conventions."                                                                                                                                                                            |

| Courier type                                | Signal and port names are shown in lowercase Courier type. Examples: data1, tdi, input. Active-low signals are denoted by suffix n, e.g., resetn.                                                                                                                                                                       |

|                                             | Anything that must be typed exactly as it appears is shown in Courier type. For example: c:\qdesigns\tutorial\chiptrip.gdf. Also, sections of an actual file, such as a Report File, references to parts of files (e.g., the AHDL keyword SUBDESIGN), as well as logic function names (e.g., TRI) are shown in Courier. |

| 1., 2., 3., and<br>a., b., c., etc.         | Numbered steps are used in a list of items when the sequence of the items is important, such as the steps listed in a procedure.                                                                                                                                                                                        |

| •••                                         | Bullets are used in a list of items when the sequence of the items is not important.                                                                                                                                                                                                                                    |

| ✓                                           | The checkmark indicates a procedure that consists of one step only.                                                                                                                                                                                                                                                     |

|                                             | The hand points to information that requires special attention.                                                                                                                                                                                                                                                         |

| CAUTION                                     | The caution indicates required information that needs special consideration and understanding and should be read prior to starting or continuing with the procedure or process.                                                                                                                                         |

| A                                           | The warning indicates information that should be read prior to starting or continuing the procedure or processes                                                                                                                                                                                                        |

| 4                                           | The angled arrow indicates you should press the Enter key.                                                                                                                                                                                                                                                              |

| •••                                         | The feet direct you to more information on a particular topic.                                                                                                                                                                                                                                                          |

xiv Altera Corporation

# Section I. SOPC Builder Features

Section I of this volume introduces the SOPC Builder system integration tool, and describes the main features. Chapters in this section serve to answer the following questions:

- What is SOPC Builder?

- What services does SOPC Builder provide?

This section includes the following chapters:

- Chapter 1, Introduction to SOPC Builder

- Chapter 2, Tour of the SOPC Builder User Interface

- Chapter 3, Avalon Switch Fabric

- Chapter 4, SOPC Builder Components

- Chapter 5, Component Editor

- Chapter 6, Archiving SOPC Builder Projects

- Chapter 7, Board Description Editor

- Chapter 8, Pin Mapper

## **Revision History**

The following table shows the revision history for Chapters 1–8.

| Chapter(s) | Date / Version       | Changes Made                                                                                                                                                         |

|------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | May 2006, v6.0.0     | No change from previous release.                                                                                                                                     |

|            | October 2005, v5.1.0 | No change from previous release.                                                                                                                                     |

|            | May 2005, v5.0.0     | No change from previous release.                                                                                                                                     |

|            | February 2005, v1.0  | Initial release.                                                                                                                                                     |

| 2          | May 2006, v6.0.0     | No change from previous release.                                                                                                                                     |

|            | October 2005, v5.1.0 | <ul> <li>Updated for the Quartus II software version 5.1.</li> <li>Added pipeline for high performance details.</li> <li>Added endian conversion details.</li> </ul> |

|            | May 2005, v5.0.0     | No change from previous release.                                                                                                                                     |

| 3          | May 2006, v6.0.0     | No change from previous release.                                                                                                                                     |

|            | October 2005, v5.1.0 | Updated for the Quartus II software version 5.1.                                                                                                                     |

|            | August 2005, v5.0.1  | <ul><li>Added burst transfer management details.</li><li>Updated pipeline management details.</li></ul>                                                              |

|            | May 2005, v5.0.0     | No change from previous release.                                                                                                                                     |

|            | February 2005, v1.0  | Initial release.                                                                                                                                                     |

Altera Corporation Section I–1

| Chapter(s) | Date / Version        | Changes Made                                                                                                                                                                                                                                              |  |

|------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4          | May 2006, v6.0.0      | No change from previous release.                                                                                                                                                                                                                          |  |

|            | October 2005, v5.1.0  | No change from previous release.                                                                                                                                                                                                                          |  |

|            | August 2005, v5.0.1   | Corrected reference to figure.                                                                                                                                                                                                                            |  |

|            | May 2005, v5.0.0      | No change from previous release.                                                                                                                                                                                                                          |  |

| 5          | May 2006, v6.0.0      | No change from previous release.                                                                                                                                                                                                                          |  |

|            | December 2005, v5.1.1 | <ul> <li>Added section "Naming Signals for Automatic Type and Interface Recognition."</li> <li>Added section "Templates for Interfaces to External Logic."</li> <li>Clarified operation of the Save command.</li> <li>Updated all screenshots.</li> </ul> |  |

|            | October 2005, v5.1.0  | No change from previous release.                                                                                                                                                                                                                          |  |

|            | May 2005, v5.0.0      | No change from previous release.                                                                                                                                                                                                                          |  |

| 6          | May 2006, v6.0.0      | Initial release.                                                                                                                                                                                                                                          |  |

| 7          | May 2006, v6.0.0      | Chapter 7 was previously chapter 6. No change to content.                                                                                                                                                                                                 |  |

|            | October 2005 v5.1.0   | Initial release.                                                                                                                                                                                                                                          |  |

| 8          | May 2006, v6.0.0      | Chapter 8 was previously chapter 7. No change to content.                                                                                                                                                                                                 |  |

|            | October 2005 v5.1.0   | Initial release.                                                                                                                                                                                                                                          |  |

Section I–2 Altera Corporation

# 1. Introduction to SOPC Builder

QII54001-6.0.0

### Overview

SOPC Builder is a powerful system development tool for creating systems based on processors, peripherals, and memories. SOPC Builder enables you to define and generate a complete system-on-a-programmable-chip (SOPC) in much less time than using traditional, manual integration methods. SOPC Builder is included in the Quartus<sup>®</sup> II software and is available to all Altera<sup>®</sup> customers.

Many designers already know SOPC Builder as the tool for creating systems based on the Nios<sup>®</sup> II processor. However, SOPC Builder is more than a Nios II system builder; it is a general-purpose tool for creating arbitrary SOPC designs that may or may not contain a processor.

SOPC Builder automates the task of integrating hardware components into a larger system. Using traditional system-on-chip (SOC) design methods, you had to manually write top-level HDL files that wire together the pieces of the system. Using SOPC Builder, you specify the system components in a graphical user interface (GUI), and SOPC Builder generates the interconnect logic automatically. SOPC Builder outputs HDL files that define all components of the system, and a top-level HDL design file that connects all the components together. SOPC Builder generates both Verilog HDL and VHDL equally, and does not favor one over the other.

In addition to its role as a hardware generation tool, SOPC Builder also serves as the starting point for system simulation and embedded software creation. SOPC Builder provides features to ease writing software and to accelerate system simulation.

This chapter introduces you to the architectural structure of systems built with SOPC Builder, and describes the primary functions of SOPC Builder.

# Architecture of SOPC Builder Systems

This section describes the fundamental architecture of an SOPC Builder system.

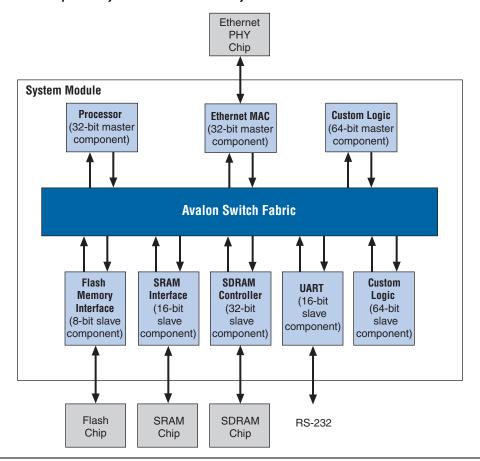

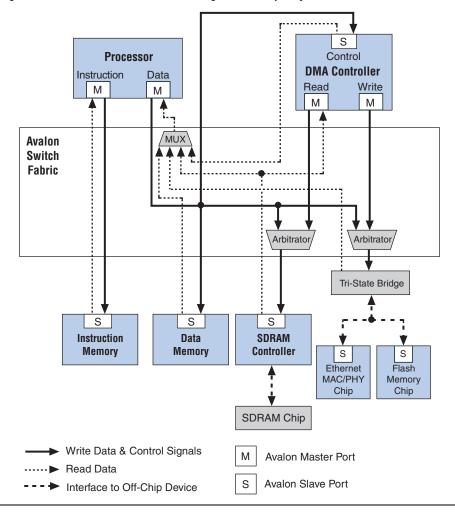

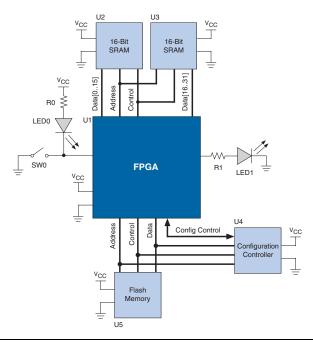

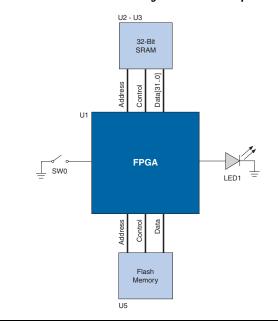

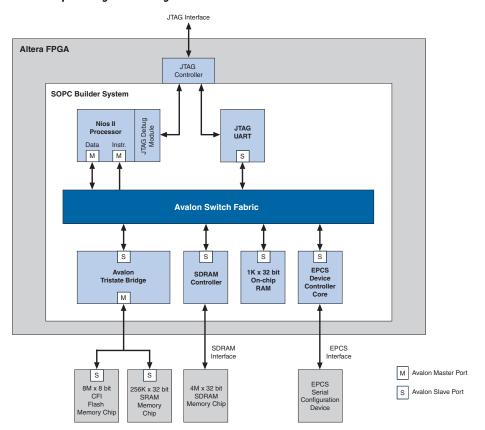

An SOPC Builder *component* is a design module that SOPC Builder recognizes and can automatically integrate into a system. SOPC Builder connects multiple components together to create a top-level HDL file called the *system module*. SOPC Builder generates *Avalon® switch fabric* that contains logic to manage the connectivity of all components in the system. Figure 1–1 shows an example of a multi-master system module with Avalon switch fabric connecting the multiple master and slave components.

Figure 1–1. Example of a System Module Generated by SOPC Builder

### **SOPC Builder Components**

SOPC Builder components are the building blocks of the system module. SOPC Builder components use the Avalon interface for the physical connection of components, and you can use SOPC Builder to connect any logical device (either on-chip or off-chip) that has an Avalon interface. The Avalon interface uses an address-mapped read/write protocol that allows master components to read and/or write any slave component.

For details on the Avalon interface, see the *Avalon Interface Specification* at www.altera.com.

A component can be a logical device that is entirely contained within the system module, such as the processor component in Figure 1–1 on page 1–2. Alternately, a component can act as an interface to an off-chip device, such as the SRAM interface component in Figure 1–1 on page 1–2. In addition to the Avalon interface, a component can have other signals that connect to logic outside the system module. Non-Avalon signals can provide a special-purpose interface to the system module, such as the Ethernet MAC in Figure 1–1 on page 1–2.

A component can be instantiated more than once per design.

Altera and third-party developers provide ready-to-use SOPC Builder components, such as:

- Microprocessors, such as the Nios II processor

- Microcontroller peripherals

- Timers

- Serial communication interfaces, such as a UART and a serial peripheral interface (SPI)

- General purpose I/O

- Digital signal processing (DSP) functions

- Communications peripherals

- Interfaces to off-chip devices

- Memory controllers

- Buses and bridges

- Application-specific standard products (ASSP)

- Application-specific integrated circuits (ASIC)

- Processors

#### SOPC Builder Ready Components

Altera awards the SOPC Builder Ready certification to intellectual property (IP) designs that have plug—and—play integration with SOPC Builder. These functions may be accompanied by software drivers, low-level routines, or other software design files.

Altera's OpenCore<sup>®</sup> and OpenCore Plus evaluation programs allow you to "test drive" an SOPC Builder component both in simulation and in hardware before you buy. You can download evaluations of Altera IP functions directly from **www.altera.com/IPMegastore**. For IP functions provided by third-party vendors, contact the vendor directly to obtain an OpenCore evaluation.

Check the Altera web site at **www.altera.com** for up–to–date information about available SOPC Builder Ready components. You can identify SOPC Builder Ready components by the logo shown in Figure 1–2.

Figure 1–2. The SOPC Builder Ready Certification Logo

#### User-Defined Components

SOPC Builder provides an easy method for you to develop and connect your own components. With the Avalon interface, user-defined logic need only adhere to a simple interface based on address, data, readenable, and write-enable signals.

You use the following design flow to integrate custom logic into an SOPC Builder system:

- 1. Define the interface to the user-defined component.

- 2. If the component logic resides on-chip, write HDL files describing the component in either Verilog HDL or VHDL.

- Use the SOPC Builder component editor wizard to specify the interface and optionally package your HDL files into an SOPC Builder component.

- 4. Instantiate your component in the same manner as other SOPC Builder Ready components.

Once you have created an SOPC Builder component, you can reuse the component in other SOPC Builder systems, and share the component with other design teams.

For instructions on developing a custom SOPC Builder component, see the *Developing SOPC Builder Components* chapter in Volume 4 of the *Quartus II Handbook*. For complete detail on the file structure of a component, see the *SOPC Builder Components* chapter in Volume 4 of the *Quartus II Handbook*. For details on the SOPC Builder component editor, see the *Component Editor* chapter in Volume 4 of the *Quartus II Handbook*.

#### **Avalon Switch Fabric**

The Avalon switch fabric is the glue that binds SOPC Builder-generated systems together. The Avalon switch fabric is the collection of signals and logic that connects master and slave components, including address decoding, data-path multiplexing, wait-state generation, arbitration, interrupt controller, and data-width matching. SOPC Builder generates the Avalon switch fabric automatically, so that you do not have to manually perform the tedious, error-prone task of connecting hardware modules.

The purpose of SOPC Builder is to abstract away the complexity of interconnect logic, allowing designers to focus on the details of their custom components and the high-level system architecture. Automatically generating the Avalon switch fabric is the keystone to achieving this purpose. Avalon switch fabric in the system module is like air for humans: Its existence is essential, but largely ignored. Because SOPC Builder generates Avalon switch fabric automatically, most users do not interact directly with it or the HDL that describes it.

For further details, see the *Avalon Switch Fabric* chapter in Volume 4 of the *Quartus II Handbook*.

# Functions of SOPC Builder

This section describes the fundamental functions of SOPC Builder.

## **Defining & Generating the System Hardware**

The purpose of the SOPC Builder GUI is to allow you to easily define the structure of a hardware system, and then generate the system. The GUI is designed for the tasks of adding components to a system, configuring the components, and specifying how they connect together.

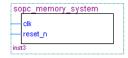

After you add all components and specify all necessary system parameters, SOPC Builder is ready to generate the Avalon switch fabric and output the HDL files that describe the system. During system generation, SOPC Builder outputs the following items:

- An HDL file for the top-level system module and for each component in the system

- A Block Symbol File (.bsf) representation of the top-level system module for use in Quartus II Block Diagram Files (.bdf)

- (Optional) Software files for embedded software development, such as a memory-map header file and component drivers

- (Optional) Testbench for the system module and ModelSim<sup>®</sup> simulation project files

After you generate the system module, it can be compiled directly by the Quartus II software, or instantiated in a larger FPGA design.

For more detail on the SOPC Builder GUI for defining and generating systems, see the *Tour of the SOPC Builder User Interface* chapter in Volume 4 of the *Quartus II Handbook*.

### Creating a Memory Map for Software Development

For each microprocessor in the system, SOPC Builder optionally generates a header file that defines the address of each slave component. In addition, each slave component can provide software drivers and other software functions and libraries for the processor.

The process for writing software for the system depends heavily on the nature of the processor in the system. For example, Nios II processor systems use Nios II processor-specific software development tools. These tools are separate from SOPC Builder, but they do use the output of SOPC Builder as the foundation for software development.

## **Creating a Simulation Model & Testbench**

You can simulate your custom systems with minimal effort immediately after generating the system with SOPC Builder. During system generation, SOPC Builder optionally outputs a push-button simulation environment that eases the system simulation effort. SOPC Builder generates both a simulation model and a testbench for the entire system. The testbench includes the following functionality:

- Instantiates the system module

- Drives all clocks and resets appropriately

- Optionally instantiates simulation models for off-chip devices

# **Getting Started**

One of the easiest ways to get started using SOPC Builder is to read the *Nios II Hardware Development Tutorial* which guides you step-by-step in building a microprocessor system, including CPU, memory, and peripherals. This tutorial and other SOPC Builder example designs are included in the Nios II Embedded Design Suite (EDS), Evaluation Edition. You can download this design suite for free from the Altera Download Center at www.altera.com.

# 2. Tour of the SOPC Builder User Interface

QII54002-6.0.0

This chapter provides reference on how to access the features available in the SOPC Builder graphical user interface (GUI). This chapter will familiarize you with the main features of the SOPC Builder GUI.

Due to evolution and improvement of the software, the figures in this chapter may not match exactly what you see in the software.

# Starting SOPC Builder

Each SOPC Builder system is associated with one Quartus<sup>®</sup> II project. Therefore, to launch SOPC Builder, you must first open a project in the Quartus II software. With a Quartus II project open, you can launch SOPC Builder by choosing **SOPC Builder** (Tools menu) or by clicking the **SOPC Builder** toolbar button. See Figure 2–1.

Figure 2-1. SOPC Builder Toolbar Button

The SOPC Builder toolbar button might not appear by default. To enable it, use the **Customize** window (Tools menu).

## Starting a New SOPC Builder System

If an SOPC Builder system does not exist in the current Quartus II project directory, SOPC Builder will display the **Create New System** dialog as shown in Figure 2–2 on page 2–2, and prompt you to specify the following:

- A name for the new SOPC Builder system This serves as the name of the system module that SOPC Builder will generate.

- Target HDL This setting determines the output language of the system module.

Figure 2–2. Create New System Dialog

### **Working with SOPC Builder Systems**

SOPC Builder operates on exactly one system at a time, and the system must be associated with a Quartus II project. A Quartus II project may have multiple associated SOPC Builder systems, but typically will have only one (if any).

If you integrate multiple SOPC Builder system modules in one Quartus II project, you must make sure all components are named uniquely across all system modules. Otherwise, filename collision will occur.

In SOPC Builder, you can create a new system by choosing **New System** (File menu). You can switch to a different system by choosing **Open System** (File menu).

SOPC Builder saves files in the same directory as the Quartus II project. Each SOPC Builder system is represented by a file named <system module name>.ptf, which is a plain-text file describing the structure of the system and other system-specific details. In a purely mechanical sense, the SOPC Builder GUI is a .ptf file editor.

Changes you make in the SOPC Builder GUI are saved immediately to the .ptf file. When you open a system, SOPC Builder creates a back-up file named <system module name>.ptf.bak, in case you need to revert changes.

# System Contents Tab

SOPC Builder employs a tabbed user interface. Tasks are categorized by function, and related tasks are presented on the same tab.

The **System Contents** tab is displayed when you open SOPC Builder. It is the view of SOPC Builder that you will use most often. You use the **System Contents** tab to do the following:

- Add components to a system

- Configure the components

- Specify connections between components

Figure 2–3 lists the elements of the **System Contents** tab. See Table 2–1 on page 2–4 for details.

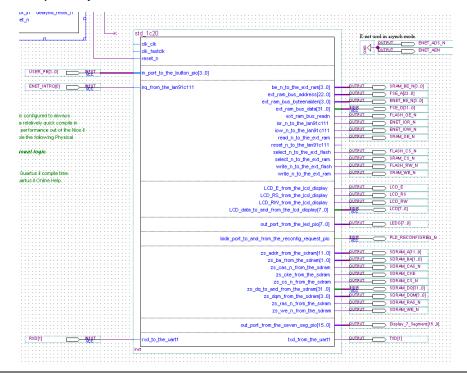

Tabs **Board Settings** Clock Settings Table Altera SOPC Builder\_full\_1c20 File Module System View Tools Help System Contents Board Settings Nios II More "cpu" Settings System Generation 🛓 Altera SOPC Builder Reate New Component... Clock Source MHz Pipeline Board: Nios Development Board, Cyclone (EP1C20) - Avalon Components sys\_clk c0 from conn... 50.0 Nios II Processor - Altera Corpor pld\_clkout e0 from conn.. **⊞** Bridges pld\_clockinput External 50.0 Communication JTAG UART Use Module Name Input Clock IRQ Description Base End SPL(3 Wire Serial) V - cpu Nios II Processor - Altera Corpora UART (RS-232 serial port) nstruction maste Master port Display ightly\_coupled\_instruction\_m... Master port + FP1C20 Nios Development Board Master port IRQ 31 lata master t Board ightly\_coupled\_data\_master\_0 Master port List of Available nt Board tag\_debug\_module 0x02120000 0x021207FF nt Board Components V htly\_coupled\_instruction... On-Chip Memory (RAM or ROM) sys clk : II Editio Slave port **≙** 0x040000 0x04000FFF nt Board Slave port **≙** 0x040000. 0x04000FFF Ethernet **⊞ http\_coupled\_data\_mem...** On-Chip Memory (RAM or ROM) injhtly\_coupled

d ma

d tha

ext\_ram\_bus

ext\_flash

ext\_ram

d t\_ram

ext\_ram

ext\_ram sys\_clk Extra Utilities DMA sys\_clk 0x02120800 0x0212081F ■ Legacy Components Avalon Tristate Bridge sys\_clk ■ Memory Flash Memory (Common Flash Int... **≜** 0×000000.. 0x007FFFFF Cypress CY7C1380C SSRAI 0x020FFFFF IDT71V416 SRAM ⊕ 0x020000... EPCS Serial Flash Controller EPCS Serial Flash Controller sys\_clk 0x02100000 0x021007FF 5 Flash Memory (Common Flas LAN91c111 Interface (Ethernet) 0x02110000 0x0211FFFF 6 IDT71V416 SRAM -⊞ sys\_clk\_tim -⊞ tag\_uart Interval timer sys\_clk 0x02120820 0x0212083F 0 JTAG UART 0x021208D0 0x021208D7 1 sys\_clk –⊞ button\_pio –⊞ ed\_pio –⊞ od\_display Installed Co PIO (Parallel I/O) sys\_clk 0x02120880 0x0212088F **(1) (0)** PIO (Parallel I/O) 0x02120890 0x0212089F sys\_clk Character LCD (16x2, Optrex 162... 0x021208A0 0x021208AF Check ▲ Move Un ▼ Move Down cpu was generated with full capabilities and must be compiled in Quartus II with the same license. cpu: The reset address points to volatile memory. Execution of Done checking for updates. Exit <u>N</u>ext Component Filters Connection Panel Messages Window Table of Active Components

Figure 2-3. Elements of the System Contents Tab

Table 2–1 describes the GUI elements shown in Figure 2–3.

| Table 2–1. GUI Elements on the System Generation Tab |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GUI Element                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Tabs                                                 | Categorizes GUI controls, based on task.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| List of Available<br>Components                      | Lists the library of available SOPC Builder components, organized by category.  Each component appears with a colored dot next to its name. The colors of the dots have the following meanings:  Green dot – A full, licensed version of the component is installed.  Yellow dot – A limited, evaluation version of the component is installed.  White dot – This component is available from Altera or a partner vendor, but is not installed.                                                                                                                                                                                                                                                                                                         |

| Component Filters                                    | Filters which type of components appear in the list of available components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Table of Active<br>Components (1)                    | Lists the components instantiated in the current system, and allows you to specify the following:  Name for each component instance  Base address for each slave port  Clock source for each component instance  Interrupt priority (if any) for each slave port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Connection Panel (1)                                 | Represents connections between the components, and allows you to perform the following:  Specify connections between master ports and slave ports.  Specify arbitration shares for slave ports that are shared by multiple master ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Board Settings                                       | <ul> <li>Allows you to specify details regarding the target hardware platform:</li> <li>Board - If the target board is known and you have an SOPC Builder board description, you can specify the target board. The board setting provides SOPC Builder with information about the target hardware, such as pin-outs and connections to off-chip devices.</li> <li>Device Family - If the target board is not known, you can specify a particular device family, which affects the behavior of certain components.</li> <li>HardCopy Compatible - Certain components have limited functionality when targeting Altera HardCopy devices. This option allows you to use only components and settings that are compatible with HardCopy devices.</li> </ul> |

| Clock Settings Table                                 | Allows you to define the clock signals used in the system module. For each clock in the clock settings table, you can specify:  Name  Source - Clock signals can be provided from an external source, or can be generated by a component inside the system module.  Frequency in MHz  Pipeline for high performance - SOPC Builder can pipeline the Avalon switch fabric for the clock domain, which improves f <sub>MAX</sub> performance.                                                                                                                                                                                                                                                                                                             |

| Messages Window                                      | Displays information, warning, or error messages related to the current system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

### Note for Table 2–1:

(1) Options available in the View menu alter how this element is displayed.

You can connect any master port to any slave port, as long as they use the same interface protocol. If they use different interface protocols, they must communicate through a bridge component, such as the AHB-to-Avalon® bridge provided with SOPC Builder.

### Adding a Component to the System

To add a component to the system, find the component in the list of available components and do one of the following:

- Double-click the component.

- Select the component, then click Add.

- Right-click the component and choose **Add New** <*component name*>.

If the component has any parameterized features, a wizard will appear allowing you to configure this instance of the component. Figure 2–4 shows an example of a configuration wizard for the SDRAM controller included with the Quartus II software.

SDRAM Controller - sdram Presets: single Micron MT48LC4M32B2-7 chip v Memory Profile Timing SDRAM Timing Parameters 01 02 03 CAS latency cycles Initialization refresh cycles Issue one refresh command every 15.625 us Delay after powerup, before initialization 100 us Duration of refresh command (t\_rfc) ns 20 Duration of precharge command (t\_rp) ทธ ACTIVE to READ or WRITE delay (t\_rcd) 20 ns Access time (t\_ac) 5.5 ns 14 Write recovery time (t\_wr, No auto precharge) Cancel < Prev Finish

Figure 2–4. SDRAM Controller Configuration Wizard

Like the overall SOPC Builder GUI, component configuration wizards use tabs to categorize GUI features, and have a message window that displays dynamic information about the current configuration of the component.

The parameters and information displayed in the configuration wizard depend on the component. Many wizards provide tool tips that give you information on how to specify each parameter.

You can open component documentation from within SOPC Builder. Right-click the component in the list of available components, and choose one of the document items listed.

### Specifying Connections, Base Address, Clock & IRQ

After you add a component, you must configure how it fits within the system.

#### Connection Panel

In the connection panel you specify the master-slave connections between components.

Each SOPC Builder component can have one or more master and slave ports. Each slave port must be connected to a master port.

Hovering the mouse over the connection panel displays the potential connection points between components, represented as dots connecting wires. A filled dot shows that a connection is made; an open dot shows a potential connection point that is not currently connected. Clicking a dot toggles the connection status. See Figure 2–5.

Figure 2-5. Connection Panel

You can connect any master port to any slave port, as long as the ports use the same type of hardware interface. If they use different interfaces, they must communicate through a bridge component, such as the AHB-to-Avalon bridge provided with SOPC Builder.

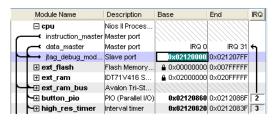

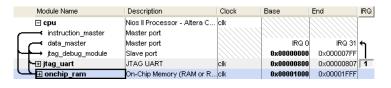

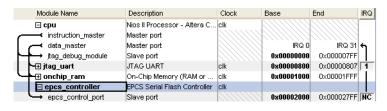

### Table of Active Components

After your component is connected in the connection panel, you use the table of active components to specify the parameters listed in Table 2–2.

| Table 2–2. Table of Active Components |                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                             | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

| Name                                  | Name of the instance of the component. SOPC Builder assigns a default name when you add a new component. To change this name, right click the component name and select <b>Rename</b> .                                                                                                                                                                                                                             |

| Use                                   | Enables/Disables the component in the current system. Turning off the <b>Use</b> setting is equivalent to removing the component from the system.                                                                                                                                                                                                                                                                   |

| Clock                                 | Clock source for the component. You must choose one of the clocks defined in the clock settings table.                                                                                                                                                                                                                                                                                                              |

| Base (1)                              | Base address where the slave port will appear in the master port's address space. SOPC Builder can automatically choose new base address values to avoid conflicts between all components.                                                                                                                                                                                                                          |

|                                       | You can automatically assign base addresses for all components by choosing <b>Auto-Assign Base Addresses</b> (System menu).                                                                                                                                                                                                                                                                                         |

|                                       | You can lock the base address on a component so that SOPC Builder will not change it automatically. To lock the base address, right-click the component in the table of active components, and choose <b>Lock Base Address</b> .                                                                                                                                                                                    |

| IRQ (1)                               | Specifies the IRQ value the slave drives to the master, if the slave port can generate interrupts. If you specify <b>NC</b> for an IRQ value, SOPC Builder will not connect interrupt signals from slave to master.  SOPC Builder can automatically choose new IRQ values to avoid conflicts between all components. To automatically assign IRQs for all components, choose <b>Auto-Assign IRQs</b> (System menu). |

#### *Note to Table 2–2:*

(1) This setting applies to slave ports only.

SOPC Builder automatically chooses defaults for these parameters when you add each component, but you must verify that they are appropriate for your system.

## **Creating User-Defined Components**

You can use the SOPC Builder component editor to create a component from user-defined logic. To open the component editor, choose **New Component** (File menu) or select **Create New Component** in the list of available components, and click **Add**.

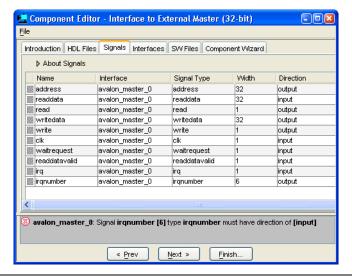

Figure 2–6 shows an example of the component editor editing a 32-bit master component.

Figure 2-6. SOPC Builder Component Editor

After creating a user-defined component, the process to instantiate the component is the same as for any other component.

For instructions on developing a custom SOPC Builder component, see the *Developing SOPC Builder Components* chapter in Volume 4 of the *Quartus II Handbook*. For complete detail on the file structure of a component, see the *SOPC Builder Components* chapter in Volume 4 of the *Quartus II Handbook*. For details on the SOPC Builder component editor, see the *Component Editor* chapter in Volume 4 of the *Quartus II Handbook*.

# System Dependency Tabs

Certain components must be configured based on system-level factors external to the component. SOPC Builder provides system dependency tabs, which allow further configuration of a component beyond the component's configuration wizard. System dependency tabs are titled More "<Name of component instance>" Settings, and appear next to the System Contents tab.

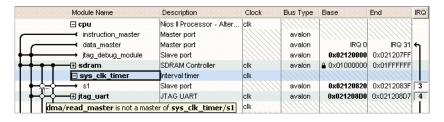

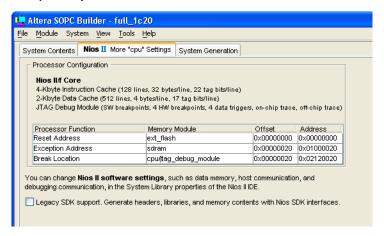

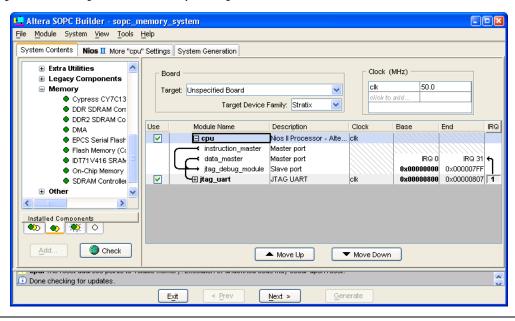

Figure 2–7 shows an example of the system dependency tab for an instance of the Nios<sup>®</sup> II processor named cpu. In this example, the Nios II processor reset and exception addresses depend on memory components in the system but external to the processor, and therefore uses a system dependency tab.

Figure 2–7. System Dependency Tab for a Nios II Processor

# Board Settings Tab

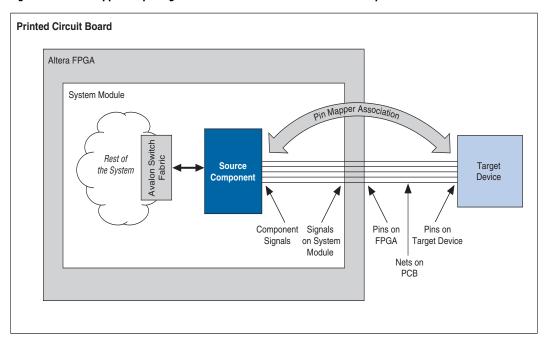

The **Board Settings** tab provides board-specific settings for the target hardware platform. SOPC Builder displays a **Board Settings** tab only if you specify a target board on the **System Contents** tab.

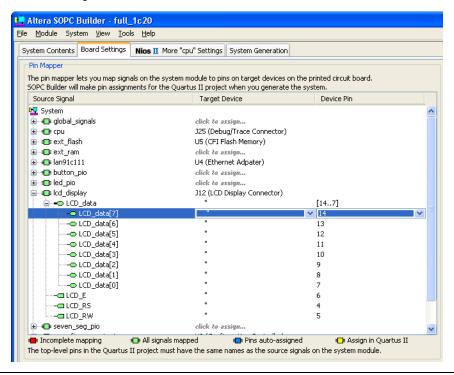

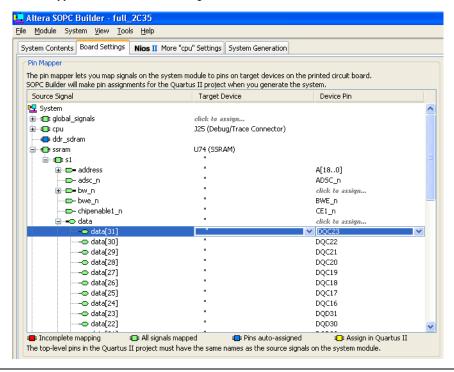

The main feature of the **Board Settings** tab is the SOPC Builder pin mapper. The pin mapper simplifies the process of assigning FPGA pins. You use the pin mapper to map logical connections between system components and devices mounted on the PCB. Based on your pin mapper settings, SOPC Builder applies appropriate pin assignments to your Quartus II project.

In addition to accelerating the process of assigning FPGA pins, the pin mapper provides a level of assurance that you have accounted for the pin assignments required for a target board. Figure 2–8 on page 2–10 shows an example of the pin mapper for a target board.

Figure 2-8. Board Settings Tab

# System Generation Tab

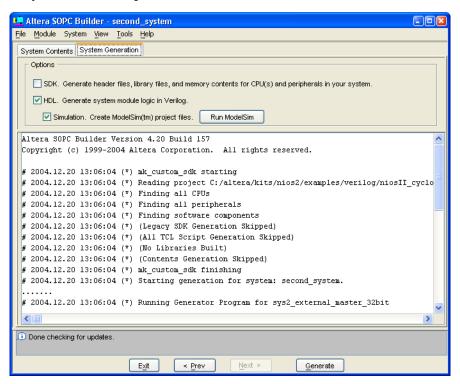

This section describes the settings available on the **System Generation** tab, and discusses the various outputs of SOPC Builder. System generation refers to SOPC Builder's process of generating output files that describe your system, based on the parameters you specified in the SOPC Builder GUI.

Figure 2–9 shows an example of the **System Generation** tab.

Figure 2-9. System Generation Page

Some SOPC Builder components, such as the Nios II processor, may modify the available options on this page.

Depending on the options on the **System Generation** tab, SOPC Builder generates the following outputs:

- Hardware design files

- Simulation model, testbench, and ModelSim<sup>®</sup> project files

- Files for software development

## **System Generation Tab Options**

This section describes each of the options available on the **System Generation** tab.

#### SDK Option

When the **SDK** option is turned on, during system generation SOPC Builder creates a custom software development kit (SDK) directory in the Quartus II project directory for each CPU in the system. The SDK contains a memory map and software files (drivers, libraries, and utilities) for any system components that provide software support files.

The Nios II processor provides a different software development flow, and therefore does not use the **SDK** option.

SDK files are arranged into the following directories:

- inc This directory contains header files. These files include the definition for the memory map, register declarations for included peripherals, and macros that can be used in creating embedded software applications.

- lib This directory contains software library files. During system generation, processor components can include commands to have SOPC Builder compile the libraries automatically.

- src This directory provides a location for application source code development. Example source code files associated with peripherals may also be copied into this directory during system generation.

Every time you generate or update the system hardware module, you must give the SDK files to the software engineers developing application code.

If you edit the files generated by SOPC Builder, save them with a unique filename to prevent the file from being overwritten in a subsequent system generation.

#### HDL Option

When the **HDL** option is turned on, during system generation SOPC Builder creates HDL files that describe the system, and stores them in the Quartus II project directory. The HDL files contain the following:

- The top-level system module

- An instance of every component in the system

- The Avalon switch fabric tailored to connect all components in the system

- A simulation model and a simulation testbench, depending on the Simulation option. See "Simulation Option" on page 2–13 for more details.

SOPC Builder outputs the top-level system module file in either Verilog HDL or VHDL, depending on which language you specified when starting SOPC Builder. However, some SOPC Builder components may provide source files in only one language.

#### Simulation Option

When the **Simulation** option is turned on, during generation SOPC Builder creates a simulation model and a test bench for the system. Simulation-specific files are written to a simulation directory in the Quartus II project directory, separate from the synthesizable HDL files.

The testbench is tailored to the structure of system module. The testbench provides the following functionality:

- Instantiates the system module

- Drives clock and reset inputs with default behaviors

- Instantiates and connects the simulation models provided for any components external to the system module, such as memory models

Individual components may also provide simulation files, which SOPC Builder copies into the simulation directory during system generation.

SOPC Builder generates a ModelSim project directory that includes the following files:

- A ModelSim Project File (.mpf) for the current system

- Simulation data files for all memory components that have initialized contents

- A setup\_sim.do file that contains setup information and aliases customized for simulating the system module

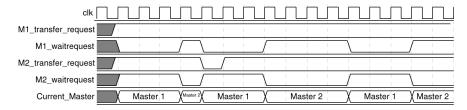

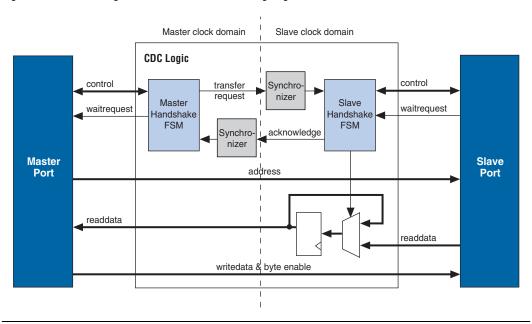

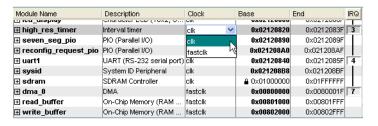

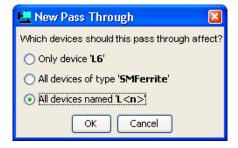

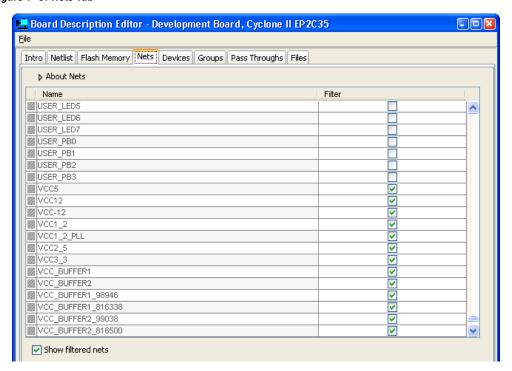

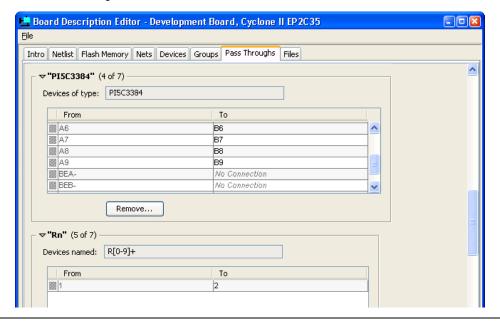

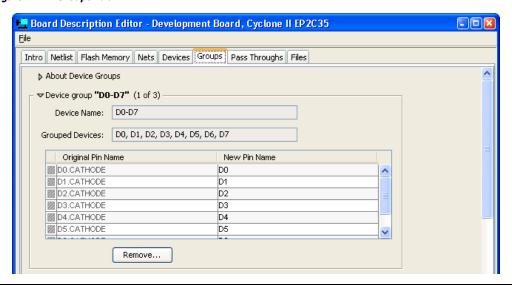

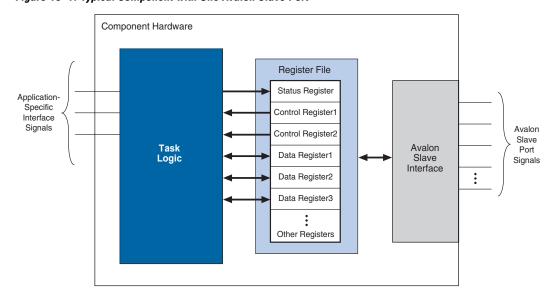

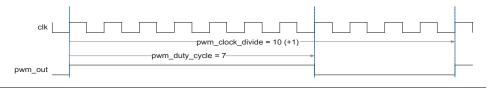

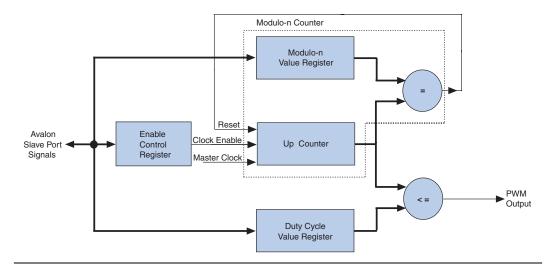

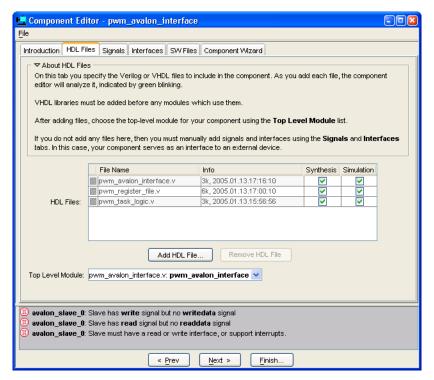

- A wave\_presets.do file that automatically displays a default set of useful waveforms